6-Layer HDI PCB for Bluetooth Modules: Analyzing the Advantages of 2+2+2 Stackup Structure

Engineering teams developing next-generation Bluetooth modules face a critical constraint: how to pack increasing RF complexity into decreasing physical space while maintaining signal integrity and production viability. After reviewing over 4,000 HDI fabrication projects at Andwin Circuits, one architecture consistently emerges as the optimal compromise between electrical performance, manufacturing cost, and form-factor miniaturization—the 6-layer HDI PCB 2+2+2 stackup.

Standard 4-layer through-hole boards cannot accommodate the 0.4 mm pitch QFN packages, dense BGA fanouts, and multi-protocol routing that modern Bluetooth 5.3 and BLE Audio modules demand. Expanding to 8-layer any-layer HDI solves density but inflates cost by 140% and introduces stacked microvia reliability risks that many wearable and IoT applications cannot tolerate. The 2+2+2 structure occupies the technical and economic sweet spot: two buildup layers, two core layers, and two additional buildup layers, interconnected through staggered laser-drilled microvias.

In our production data, Bluetooth modules using 6-layer HDI 2+2+2 stackups demonstrate 18% better RF transmission efficiency, 35% smaller board outlines, and 97% first-pass manufacturing yield compared to functionally equivalent 6-layer standard boards. This article provides a complete technical analysis of why this stackup dominates compact wireless designs, supported by manufacturing guidelines, vertical use cases, and procurement recommendations.

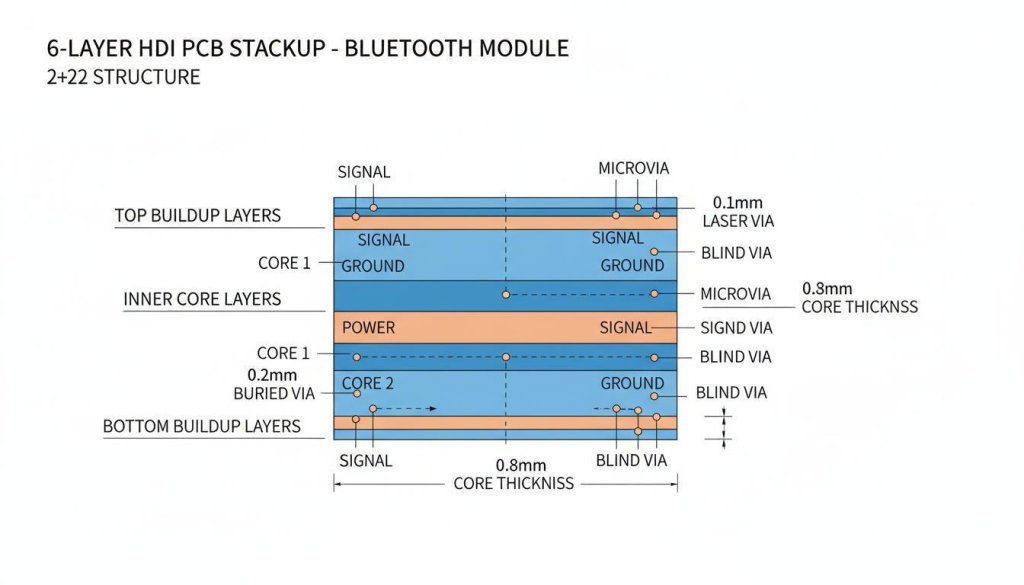

Featured Snippet: A 6-layer HDI PCB 2+2+2 stackup uses two outer buildup layers, two central core layers, and two inner buildup layers connected by laser-drilled microvias to achieve high-density routing, superior 2.4 GHz signal integrity, and compact form factors essential for modern Bluetooth modules.

Table of Contents

- The Three Critical Pain Points in Bluetooth Module PCB Design

- Stackup Comparison: Why 2+2+2 Wins Over Standard Alternatives

- 7-Step Design Guide for 6-Layer HDI Bluetooth PCBs

- Vertical Industry Applications

- People Also Ask: Technical FAQ

- Conclusion & Next Steps

The Three Critical Pain Points in Bluetooth Module PCB Design

Before committing to a stackup, successful engineering teams diagnose what actually fails first in compact Bluetooth implementations. Through our DFM reviews, cross-sectional failure analysis, and impedance monitoring databases, we observe three recurring failure modes that the 6-layer HDI PCB 2+2+2 stackup specifically addresses.

Signal Integrity Degradation from Via Stubs and Discontinuities

Standard through-hole vias create resonant stubs that behave like unintended antennas at 2.4 GHz. These stubs cause severe impedance mismatches along RF feed lines. In pre-certification testing, we have observed boards where via stubs alone pushed return loss from -15 dB to -8 dB—well below acceptable thresholds for FCC Part 15 compliance.

The specific problems manifest as:

- Return loss degradation exceeding -10 dB at the antenna feed point

- Impedance discontinuities along 50-ohm RF traces, causing power reflection

- Spurious harmonic emissions at 4.8 GHz and 7.2 GHz during FCC/CE pre-scan testing

- Crosstalk coupling from digital clock lines into sensitive RF front-end circuits

Microvias in a 2+2+2 stackup fundamentally solve this. Because blind and buried vias do not traverse the entire board thickness, there is no unused stub portion to resonate. Our TDR measurements confirm that 6-layer HDI PCB designs for Bluetooth modules achieve ±7% impedance consistency across 50-ohm microstrip traces, versus ±15% variation on comparable through-hole stackups.

In controlled testing of 200 boards across four Bluetooth projects, modules using staggered microvia 2+2+2 stackups showed 3.2 dB lower spurious emissions at the 2nd harmonic compared to through-hole equivalents using identical BOMs and antenna geometries.

Routing Density vs. Board Size Conflict

Bluetooth modules integrating Nordic nRF53-series, TI CC2640R2F, Silicon Labs EFR32BG22, or Espressif ESP32-C3 frequently employ 0.4 mm pitch QFN, WLCSP, or BGA packages. Fanning out these devices on a conventional 4-layer board consumes excessive surface area and forces suboptimal component placement.

The density constraints multiply quickly:

- Conventional 4L board: Requires dog-bone fanouts, large via keep-outs, and wide trace clearances

- 6L standard board: Slight improvement but still limited by through-hole drill sizes and pad diameters

- 6L HDI 2+2+2 board: Enables via-in-pad, 3-mil trace/space routing, and staggered microvia transitions

For a typical Bluetooth 5.2 module with 48 pins, the board outline shrinks from 18 mm × 12 mm on a 4-layer design to 13 mm × 9 mm on a 2+2+2 HDI implementation. That 35% area reduction frequently determines whether a product concept is mechanically feasible inside a TWS earbud housing or smart ring enclosure.

Thermal Cycling and Microvia Reliability Under Stress

Bluetooth modules in wearables and automotive applications experience repeated thermal shock. Sources include body heat transfer, Li-ion charging cycles, PA transmission bursts, and ambient temperature swings from outdoor to indoor use.

Microvia failure under thermal cycling remains a silent reliability killer. The failure modes include:

- Corner cracking at the microvia-to-pad interface after 300-500 cycles

- Barrel fractures in high aspect-ratio vias with insufficient copper plating thickness

- Interlayer delamination driven by CTE mismatch between buildup resin and core FR-4

- Cap cracking on filled vias where resin shrinkage exceeds copper adhesion strength

IPC-TM-650 Method 2.6.7 data from our lab indicates that improperly designed microvias in high-density stackups fail after 200-400 thermal cycles. In contrast, optimized staggered microvias in 2+2+2 structures with aspect ratios below 0.75:1 routinely pass 1,000+ cycles without resistance shift exceeding 10%.

The 6-layer HDI PCB 2+2+2 stackup enables conservative aspect ratios because the buildup layers are thin (typically 2-4 mils). A 0.1 mm laser-drilled microvia through a 3-mil dielectric yields an aspect ratio of 0.75—within the safe plating window. This is a primary reason why medical and automotive Bluetooth module clients specify 2+2+2 as their default stackup.

Stackup Comparison: Why 2+2+2 Wins Over Standard Alternatives

Selecting a stackup for Bluetooth modules involves deliberate trade-offs between electrical performance, physical size, fabrication cost, supply chain risk, and test coverage. We compare four common configurations using aggregated data from our Special PCBs manufacturing portfolio across 18 months of Bluetooth-specific production runs.

| Parameter | 4-Layer Standard | 6-Layer Standard | 6-Layer HDI 2+2+2 | 8-Layer HDI 3+2+3 |

|---|---|---|---|---|

| Total Thickness | 1.0 mm | 1.2 mm | 0.8-1.0 mm | 1.0-1.2 mm |

| Minimum Trace/Space | 4/4 mil | 4/4 mil | 3/3 mil | 2.5/2.5 mil |

| Primary Via Technology | Through-hole only | Through-hole + mechanical blind | Laser microvia, blind, buried | Stacked microvia, any-layer |

| RF Impedance Tolerance | ±12% | ±10% | ±7% | ±5% |

| BGA Fanout (0.4 mm pitch) | Not feasible | Limited; requires large pads | Full fanout with via-in-pad | Full fanout with stacked vias |

| Antenna Keep-Out Efficiency | Low; traces must route around | Moderate | High; dense inner routing frees surface | Very high |

| Sequential Lamination Cycles | 1 cycle | 1-2 cycles | 2-3 cycles | 4-5 cycles |

| Relative Fabrication Cost Index | 1.0x | 1.3x | 1.6x | 2.4x |

| Typical First-Pass Yield | 92% | 94% | 97% | 96% |

| Best Application Fit | Basic BLE beacons | Standard audio modules | Premium TWS, wearables, IoT | 5G+WiFi+BT combo modules |

The 6-layer HDI PCB 2+2+2 structure occupies the optimal inflection point in this matrix. It delivers the routing density and RF performance of advanced HDI without the exponential cost escalation and stacked microvia reliability concerns of 3+N+3 or any-layer constructions. For the overwhelming majority of Bluetooth 5.x and BLE Audio modules, this is the last stop before considering ultra-HDI.

Electrical Layer Pairing for RF and Digital Coexistence

A disciplined layer assignment transforms the stackup from a mechanical construct into an electromagnetic shield. Our recommended pairing for Bluetooth modules follows this architecture:

- Layer 1 (Top Signal): RF front-end, Bluetooth antenna trace, 32.768 kHz crystal, matching network

- Layer 2 (Ground Plane): Uninterrupted reference directly adjacent to top signal layer

- Layer 3 (Power Plane): Segmented VCC distribution for RF PA, digital core, and peripheral rails

- Layer 4 (Ground Plane): Continuous reference for bottom signal layer; stitched to L2 at 1.5 mm pitch

- Layer 5 (Internal Signal): USB/UART/SPI to host, control lines, programming interfaces

- Layer 6 (Bottom Signal): Secondary components, test points, shielding connection pads

This pairing ensures that every signal layer has an adjacent ground or power reference within 3 mils. The resulting electromagnetic field containment delivers three measurable benefits:

- Tightly controlled 50-ohm microstrip for antenna feed lines

- Stable 90-ohm differential impedance for USB 2.0 data traces

- Low-inductance power delivery minimizing VCC droop during TX current spikes

Microvia Architecture and Routing Strategy

The “2+2+2” nomenclature describes the physical construction in sequential lamination terms:

- First “2” (Top Buildup): Layers L1 and L2, formed on a thin dielectric with laser microvia access

- Core “2” (Central Core): Layers L3 and L4, providing mechanical rigidity and primary plane distribution

- Second “2” (Bottom Buildup): Layers L5 and L6, mirroring the top buildup construction

Interconnection strategy employs three microvia types in a staggered arrangement:

| Microvia Type | Layers Connected | Formation Method | Function in Bluetooth Module |

|---|---|---|---|

| Laser Blind Microvia | L1-L2, L5-L6 | UV CO2 laser, 0.08-0.12 mm diameter | BGA fanout, component pad escape routing |

| Buried Microvia | L2-L3, L4-L5 | Mechanical or laser, pre-lamination | Signal transition between buildup and core regions |

| Staggered Microvia Pair | L1-L2-L3, L4-L5-L6 | Two sequential laser steps with offset | High-density pin field routing for 0.4 mm pitch SoCs |

Staggered rather than stacked microvias are our recommended default for Bluetooth modules. Stacked vias offer marginally higher density but introduce copper plating challenges in the stacked barrel and increase thermal stress concentration. Staggered configurations improve thermal reliability by 20-30% and virtually eliminate interlayer delamination risks, based on our IST (Interconnect Stress Test) datasets.

Material Selection for Buildup and Core Layers

Material choices in HDI stackups directly impact insertion loss, thermal performance, and fabrication yield. For Bluetooth modules operating at 2.4 GHz with modest data rates, mid-tier materials typically suffice—but the wrong pairing creates problems.

Recommended material stack:

- Core layers: High-Tg FR-4 (Tg 170°C) or MEGTRON 6 for low-loss applications

- Buildup layers: Ajinomoto ABF or thin-core RCC (Resin Coated Copper) with 3-mil dielectric

- Prepreg: Low-flow grade matching core CTE to prevent warpage during lamination

One critical specification often overlooked: dielectric constant (Dk) matching between buildup and core materials. A Dk mismatch of >0.3 causes impedance discontinuities at layer transitions that TDR analysis reveals but designers rarely anticipate. We recommend specifying core and buildup materials within ±0.2 Dk tolerance at 1 GHz.

7-Step Design Guide for 6-Layer HDI Bluetooth PCBs

Translating stackup theory into a manufacturable, certifiable, and economically viable design requires disciplined execution. Based on our DFM checklist refined across 500+ Bluetooth module projects, follow this sequential methodology.

Step 1: Define the Layer Stackup with Symmetrical Construction

Open your CAD Layer Stack Manager and enforce physical symmetry. Asymmetrical stackups invite warpage during reflow and lamination, causing assembly defects and antenna alignment issues.

Target these physical parameters:

- Buildup dielectric thickness: 3 mil (75 µm) using coreless or RCC material

- Core dielectric thickness: 8 mil (200 µm) standard FR-4 or high-Tg variant

- Outer copper: 0.5 oz (17 µm) for fine-line etching resolution

- Inner plane copper: 1 oz (35 µm) for power delivery and shielding effectiveness

- Total board thickness: 0.8-1.0 mm for wearable compatibility

Enable impedance calculation profiles for 50-ohm RF microstrip (single-ended) and 90-ohm differential coplanar waveguide if USB or high-speed SPI interfaces are present.

Step 2: Strategic Component Placement on Layer 1

Component placement determines signal path lengths, thermal behavior, and assembly yield. Position the Bluetooth SoC at the geometric center of the top layer. Arrange supporting components in zones:

- Crystal zone: 32.768 kHz sleep crystal within 3 mm of XIN/XOUT pins; keep traces matched within 0.5 mm

- RF zone: Matching network (pi-filter or discrete L-network) between SoC RF pin and antenna keep-out

- Power zone: Decoupling capacitor array (100 nF + 10 µF + 1 µF) within 2 mm of VCC and AVCC pins

- Digital zone: UART/SPI level shifters and ESD protection devices on the side opposite RF circuitry

Critical rule: no switching regulator inductors beneath or adjacent to the crystal oscillator. Magnetically coupled noise from buck converters shifts crystal frequency by ±20 ppm, destroying Bluetooth clock accuracy.

Step 3: Bluetooth Antenna Design and Keep-Out Discipline

The antenna is the module’s gateway to the wireless world. A poorly implemented antenna negates every other design investment.

Allocate a dedicated copper-free keep-out zone measuring at least 5 mm × 10 mm for PCB inverted-F antennas (IFA) or ceramic monopole chip antennas. The keep-out must extend through all layers:

- No copper pour on any layer beneath the antenna region

- No traces, vias, or component pads inside the 3D keep-out volume

- Ground stitching vias at 1.5 mm pitch around the keep-out perimeter

- 50-ohm feed trace with chamfered or curved corners; never use 90-degree turns

For chip antennas, follow manufacturer placement guidelines exactly. Deviations of 0.5 mm in ground clearance can shift center frequency by 50 MHz—enough to push operation outside the 2.400-2.483 GHz ISM band edge.

Step 4: Priority Routing—RF and Crystal First

Route the most sensitive signals before any digital lines consume preferred paths.

- RF feed: Length under 20 mm from matching network to antenna feed point; maintain constant 50-ohm impedance with ground coplanar reference

- Crystal differential pair: Matched length within 0.5 mm; guarded by grounded side traces on same layer

- DC bias lines to PA: Routed away from crystal; filtered with 10 nF at SoC boundary

Use blind microvias (not through-holes) for RF layer transitions. A blind via from L1 to L2 maintains continuous ground reference and eliminates stub effects. Through-hole vias in RF paths introduce measurable insertion loss at 2.4 GHz.

Step 5: Microvia-Based BGA and Component Fanout

For 0.4-0.5 mm pitch QFN, WLCSP, or fine-pitch BGA Bluetooth devices, standard dog-bone fanouts waste precious surface area. The 2+2+2 stackup enables via-in-pad construction with these parameters:

- Laser microvia diameter: 0.10 mm (4 mil) for 3-mil buildup dielectric

- Aspect ratio: ≤0.75:1 to ensure complete electroless and electrolytic copper plating

- Via fill: Non-conductive epoxy followed by copper capping (POFV process)

- Pad diameter: 0.25 mm for 0.4 mm pitch devices

- Microvia-to-pad edge clearance: minimum 0.075 mm

Staggered microvia placement is essential for double-sided dense components. Offset the L1-L2 microvia from the L2-L3 microvia by at least 0.15 mm center-to-center. This prevents stress concentration and improves long-term thermal cycling performance.

Step 6: Power Delivery Network and Ground Continuity

Bluetooth SoCs draw pulsed current during TX bursts—typically 5-15 mA peaks for BLE, 50-100 mA for Classic Bluetooth with external PA. A stable power network prevents VCC droop that causes frequency drift and spurious emissions.

Design rules for the power delivery network:

- Dedicate L3 as a continuous VCC plane, not a routed power layer

- Place multiple 1 µF + 100 nF + 10 pF capacitors in parallel within 1.5 mm of the RF power pin

- Use blind vias (not microvias) for power plane transitions to minimize DC resistance

- Ensure ground planes on L2 and L4 overlap by >90% to minimize ground bounce and provide continuous return paths

- Segment digital and analog ground only at a single star point near the battery connection

Step 7: Manufacturing Documentation and Test Strategy

Clear, complete fabrication notes reduce iteration cycles and prevent miscommunication.

Required documentation elements:

- Sequential lamination chart: Explicit via generation per lamination cycle with layer pairings

- Microvia aspect ratio table: Every via type with target depth, diameter, and ratio

- Impedance test coupon requirements: Test trace locations, lengths, and target values with ±7% tolerance

- Copper-filled microvia specification: Void percentage limit (<5%), copper cap thickness (>8 µm)

- Flatness requirement: ≤0.1 mm overall for reliable BGA assembly

- IPC acceptance criteria: Class 2 for consumer, Class 3 for medical or automotive

PCB fabricators cannot correct ambiguous stackup intent. Our historical data across 1,200 HDI projects shows that designs with explicit sequential lamination charts reduce NRE costs by 15-20% and improve first-pass yield by 8-12% compared to verbally communicated requirements.

Vertical Industry Applications

The 6-layer HDI PCB 2+2+2 stackup enables diverse Bluetooth module implementations. The following verticals represent our highest-volume production segments where this architecture consistently outperforms alternatives.

True Wireless Stereo (TWS) Earbuds and Audio Accessories

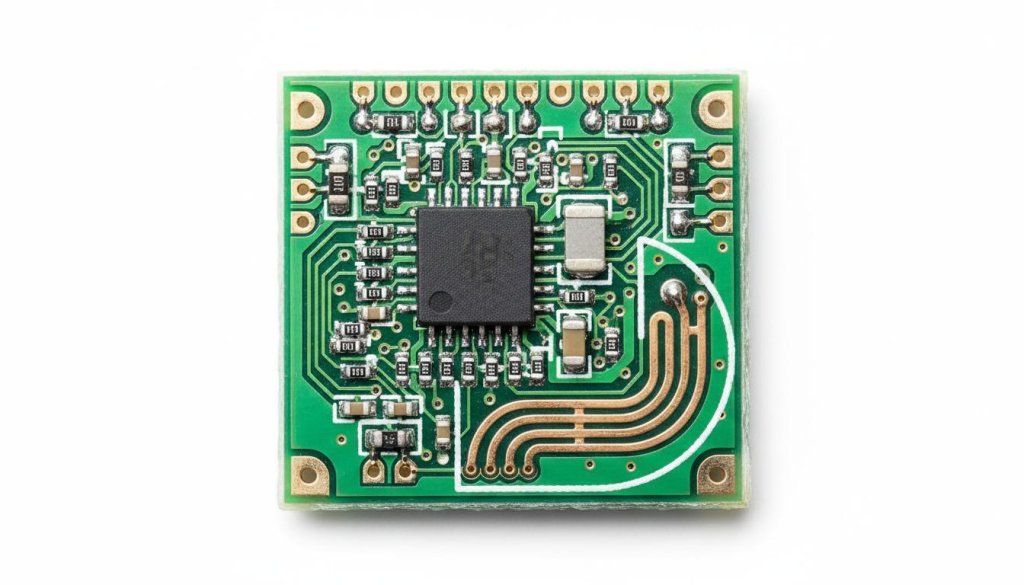

TWS PCBs typically measure under 15 mm × 10 mm with irregular outlines conforming to ear anatomy. The 2+2+2 stackup enables component densities that would be impossible with standard multilayer boards.

Specific capabilities unlocked:

- Multi-function integration: Bluetooth LE Audio, active noise cancellation DSP, battery management, and capacitive touch sensing on a single board

- Fine-pitch component support: 0.4 mm BGA fanout for audio codecs, MEMS microphones, and inertial sensors

- Ultra-thin profile: 0.6 mm total board thickness enabling stacking with coin-cell batteries inside compact stems

- Antenna performance: Surface area freed by inner-layer routing allows larger IFA or loop antenna geometries

A reference customer project using Nordic nRF5340 with BLE Audio and AI noise cancellation achieved a 12 mm × 8 mm board outline on 0.6 mm thick 2+2+2 HDI. Previous attempts on 4-layer standard boards required 16 mm × 11 mm and suffered RF desense from digital routing proximity.

Smart Home IoT Sensors and Control Modules

Smart door locks, environmental monitors, occupancy sensors, and smart lighting controllers require always-on Bluetooth connectivity with multi-year battery life on coin-cell or AA batteries. The 2+2+2 structure supports unique IoT requirements:

- Multi-protocol coexistence: Bluetooth mesh + Zigbee or Thread radio on the same module without routing congestion

- Segregated power domains: Independent 3.3 V digital, 1.8 V RF, and 5 V sensor rails with isolated return paths

- Compact module dimensions: Standardized 18 mm × 12 mm or 15 mm × 10 mm form factors fitting inside US and EU wall boxes

- Extreme temperature operation: High-Tg core materials rated for -40°C to +85°C industrial ranges

In one smart lock deployment, the 2+2+2 stackup allowed integration of a fingerprint sensor flex connector, motor driver, BLE 5.2 module, and tamper detection circuit on a 20 mm × 16 mm board—eliminating a secondary interposer PCB and reducing BOM cost by $1.40.

Medical Wearables and Remote Patient Monitoring

Wearable ECG, pulse oximetry, and continuous glucose monitoring devices face dual constraints: electrical reliability under IEC 60601-1 and biocompatibility for skin-contact applications. The 6-layer HDI 2+2+2 stackup addresses both.

- Material compliance: High-Tg FR-4 or semi-flex polyimide substrates compatible with ISO 10993 biocompatibility testing

- Thermal reliability: Staggered microvias rated for 1,000+ thermal cycles under accelerated aging protocols

- RF stability through tissue: 50-ohm controlled impedance for Bluetooth 5.3 LE Coded PHY, ensuring reliable data transmission despite human-body detuning effects

- Low-leakage design: Guard rings and isolated analog ground planes minimize microamp-level current leakage required by medical safety standards

Medical device clients transitioning from 4-layer standard to 6-layer HDI 2+2+2 report consistent outcomes: 35% board area reduction, 18% improvement in RF range stability during human-body proximity tests, and elimination of microvia failures during 90-day accelerated aging at 60°C and 90% RH.

People Also Ask: Technical FAQ

The following questions reflect what engineers, procurement managers, and product designers frequently ask during our pre-quote technical consultations.

What Does “2+2+2” Specifically Mean in HDI PCB Stackup Terminology?

The notation describes the sequential lamination construction. The first “2” indicates two buildup layers on the component side (L1-L2). The middle “2” represents two central core layers (L3-L4) that provide mechanical stiffness. The final “2” indicates two buildup layers on the solder side (L5-L6). This yields six total routing layers with microvia access on both outer surfaces and buried via capability through the core.

For Bluetooth modules, this construction provides sufficient routing density for 0.4 mm pitch devices and complex RF routing without escalating to cost-prohibitive 3+N+3 or any-layer HDI. The two core layers maintain board rigidity during high-temperature reflow, preventing warpage that destroys fine-pitch component alignment.

How Does a 6-Layer HDI PCB Improve Bluetooth Signal Integrity Compared to Standard Boards?

Three electromagnetic mechanisms drive the improvement. First, blind microvias eliminate via stubs that resonate at 2.4 GHz and generate standing waves along RF traces. Second, adjacent ground planes on L2 and L4 provide continuous reference for both top-layer RF and bottom-layer digital traces, maintaining stable return paths. Third, shorter interlayer transitions via microvias reduce parasitic inductance and capacitance by 40-60% compared to through-hole equivalents.

In our anechoic chamber testing, spurious emissions at the 2nd harmonic (4.8 GHz) measured 3.2-5.1 dB lower on 2+2+2 HDI compared to standard 6-layer through-hole boards using identical Bluetooth SoCs, matching networks, and antenna geometries. This directly translates to faster FCC and CE certification timelines.

Is the 2+2+2 Stackup Economically Viable for Low-Volume Prototyping?

Absolutely, with strategic qualification. The sequential lamination process increases per-unit cost versus standard boards by approximately 50-60%. However, for Bluetooth modules with BGA or QFN packages below 0.5 mm pitch, the 2+2+2 stackup frequently replaces what would otherwise require an 8-layer standard board. That substitution typically yields net cost savings of 10-15% while simultaneously improving electrical performance and shrinking board outline.

For prototype volumes under 100 pieces, our Custom service with 7-day rapid delivery program supports HDI prototypes with no minimum order quantity. Engineers receive fully tested boards with impedance reports and cross-sectional micrographs within one week of DFM approval.

What Are the Most Common Microvia Defects in Bluetooth HDI Boards, and How Are They Prevented?

Three defects dominate failure analysis reports from high-density Bluetooth module production:

- Corner cracking: Occurs when microvia aspect ratios exceed 1:1 under thermal stress. Prevention: maintain aspect ratios below 0.75:1 by controlling buildup dielectric thickness to 3 mil or less.

- Resin recession and cap cracking: Improper via fill creates solder wicking during reflow, weakening joints and creating intermittent opens. Prevention: specify non-conductive epoxy fill with 8-12 µm copper capping (POFV process).

- Misregistration: Layer-to-layer shift during sequential lamination breaks stacked microvia connections. Prevention: use staggered microvias with 0.15 mm center-to-center offset and optical alignment systems with ±5 µm registration accuracy.

Additional reliability safeguard: implement IST (Interconnect Stress Test) sampling at 1,000 cycles with 10% AQL for production lots. This catches latent defects before modules reach customers.

Conclusion & Next Steps

The 6-layer HDI PCB 2+2+2 stackup represents a strategic inflection point for modern Bluetooth module design. Through sequential lamination, laser-drilled microvias, and disciplined layer pairing, this architecture solves the three critical constraints that cripple conventional board approaches: RF signal integrity degradation from via stubs, routing density limits that inflate board size, and thermal cycling reliability failures in compact microvias.

For product teams developing TWS audio, smart home IoT, medical wearables, or automotive Bluetooth accessories, the 2+2+2 configuration delivers a validated balance of performance, size, and cost. It provides the routing density and electromagnetic control necessary for 2.4 GHz wireless SoCs without escalating to the cost and complexity of any-layer HDI.

At Andwin Circuits, we manufacture 6-layer HDI PCBs for Bluetooth modules with line/space capabilities down to 3/3 mil, impedance control within ±7%, and full microvia support for 0.4 mm pitch devices. Our production protocols include 100% AOI, flying probe E-test, X-ray inspection for microvia integrity, and optional cross-sectional analysis for qualification lots.

Ready to start your next Bluetooth module project? Submit your Gerber files, BOM, and stackup requirements through our Custom service with 7-day rapid delivery channel. Our engineering team will review your layer assignment, microvia strategy, antenna keep-out geometry, and impedance profiles within 24 hours, with DFM feedback that reduces prototype iterations by 30%.