Considerations and challenges of 5G technology on high-speed PCB

Considerations and challenges of 5G technology on high-speed PCB

The 5G era has arrived, and more and more mobile wireless communication systems are being upgraded and converted to adopt 5G technology to better connect to the Internet of Things (IoT). The astonishing speeds of 5G will open new market opportunities for all industries that use, design and manufacture system components and applications.

What does this mean for the high-speed PCB industry?

First, materials aspects must be prioritized when designing and building PCB stackups. 5G PCBs must meet all specifications while carrying and receiving signal transmissions, providing electrical connections, and providing controls for specific functions. Additionally, PCB design challenges will need to be addressed, such as maintaining signal integrity at higher speeds, thermal management, and how to prevent electromagnetic interference (EMI) between the data and the board.

GET PCB MANUFACTURING AND ASSEMBLY QUOTE NOW!

1. Mixed signal receiving circuit board design

Nowadays, most systems are dealing with 4G and 3G PCBs. This means that the component’s reception and reception frequency range is 600 MHz to 5.925 GHz, with a bandwidth channel of 20MHz, or 200kHz for IoT systems. When designing PCBs for 5G network systems, these components will require millimeter wave frequencies of 28GHz, 30GHz or even 77GHz, depending on the application. For wideband channels, a 5G system will handle 100MHz below 6GHz and 400MHz above 6GHz.

These higher speeds and higher frequencies will require the use of suitable materials within the PCB to capture and transmit both lower and higher signals without signal loss and EMI. There’s also the issue that devices will become lighter, more portable and smaller. With strict weight, size and space constraints, PCB materials must be flexible and lightweight to accommodate all the microelectronics on the board.

For PCB copper traces, thinner traces and tighter impedance control must be followed. The traditional subtractive etching process used for 3G and 4G high-speed PCBs can be switched to a modified semi-additive process. These improved semi-additive processes will provide more accurate traces and straighter walls.

Material substrates are also being redesigned. Printed circuit board companies are looking into materials with dielectric constants as low as 3, because standard materials for low-speed PCBs are typically 3.5 to 5.5. Tighter fiberglass weaves, lower loss factor lossy materials, and low profile copper will also be options for high-speed PCBs for digital signals, preventing signal loss and improving signal integrity.

2. EMI shielding issues

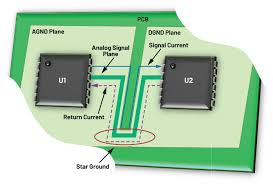

EMI, crosstalk and parasitic capacitance are major issues with circuit boards. To combat crosstalk and EMI due to analog and digital frequencies on the board, separate traces are highly recommended. Using a multilayer board will provide greater versatility in deciding how to place high-speed traces so that analog and digital return signal paths are kept away from each other while keeping AC and DC circuits separate. Adding shielding and filtering when placing components should also reduce the amount of natural EMI on the PCB.

To ensure that there are no defects on the copper surface as well as severe shorts or breaks, advanced automated optical inspection systems (AIO) and 2D metrology with higher capabilities are used to inspect the conductor traces and measure them. These technologies will help PCB manufacturers look for possible signal degradation risks.

3. Thermal management challenges

Higher signal speeds will cause the current through the PCB to generate more heat. PCB materials used for dielectric materials and core substrate layers will need to adequately handle the high speeds required by 5G technology. If there isn’t enough material, it can cause copper traces to peel, shrink, and warp as these issues can cause the PCB to deteriorate.

To handle these higher temperatures, manufacturers will need to focus on material selection that addresses thermal conductivity and thermal coefficient issues. A good PCB must be manufactured using materials with higher thermal conductivity, excellent heat transfer, and consistent dielectric constant to provide all the 5G features required for this application.

The miniaturization trend of integrated circuits forced PCB to follow suit, and eventually some ordinary products also used HDI design. While most consumers may not realize this, they probably own multiple such products that rely on HDI design and routing on the PCB. Successful placement and routing of these products depends on designing the correct HDI PCB stackup.

While any board with a high-rise count will be expensive, these products have followed the trend of packing more advanced functionality into smaller spaces. With the recently announced 1 million (25 micron) trace widths, HDI designs are getting smaller and smaller, and the limiting factors that determine routing density are layer count, net count, and component count. If you are designing advanced products that push the limits of component and wiring density, pay attention to HDI PCB stack-up before starting layout.

4.Number of layers in HDI PCB stack-up

Recently, a few questions have come up on forums that all boil down to: How many layers are used in an HDI PCB? HDI PCB stacking and wiring are generally used in boards between 8 and 24 layers. The exact number of layers depends on the required trace density, the total number of HDI nets, and the approximate space they will take up on the board.

You may also need to make room for other components that don’t necessarily require HDI cabling and need to be separated from the HDI circuit block. In the example design, multiple wireless protocols are used in an area separate from the digital portion of the board, which is built around a large FPGA. The RF section uses relatively wide traces and lots of ground isolation, while the digital section requires multi-layer cabling for over 1,000 nets and over 300 components.

With such high net counts typically found in HDI boards, how do you determine the number of layers required in an HDI PCB stackup? Assuming you are using the time-tested HDI manufacturing process, you need to estimate how many traces can be accommodated per layer board size and then add additional layers for power and ground planes. For the 1000 clear boards mentioned above, we use 10-layer boards as the initial estimate for the HDI PCB stackup. Assuming a total of 10 layers, you can calculate the thickness of each layer and use this to determine the trace width required to control impedance. The process for estimating the number of HDI PCB stack-up layers can be carried out as follows:

(1). Trace size:

First, you need to size the traces to the appropriate width and layer thickness to ensure controlled impedance. Here, a preliminary estimate of the layer thickness is required based on previous experience. Another way to do this is to look at the BGA spacing to set an upper limit on trace width, and use that value to determine the layer thickness required for the desired trace impedance.

(2.) Net per layer estimate:

Once you determine the required trace width/layer thickness (and the spacing between differential pair traces), you can roughly determine how much space the signal layers will occupy within the HDI layout area. This requires specifying a board size estimate; multiplying the approximate number of BGA breakout channels per unit area by the board area gives you the number of nets per layer. This can then be used to estimate the total number of layers required in the HDI PCB stack-up.

(3). Layer number calculation:

Once you know the number of networks required for each layer, simply divide this number by your number of networks to get a layer number. Note that this only gives you an estimate of signal layers, not the total number of layers. Now just add power and ground planes to your HDI PCB stack and you have an initial layer stack.

5.BGA sector shape and number of layers

Fine-pitch BGAs are one of the reasons some designers are forced to work under the HDI regime. Estimating the number of nets per layer is a bit difficult because you need to specify the HDI area on the board ahead of time, and the BGA breakout and escape routing strategies will limit the number of nets per layer. However, BGA breakout patterns are created in a “grid” pattern with a fixed number of traces per layer, depending on where those traces are spread out. Traditional dog bone fanning and tented micro holes in the case of pad fanning strategy. Typically, two rows of pads can be extracted from a high-density BGA at a time, or three rows if using very narrow traces.

The dogbone scalloping strategy on the surface is suitable for mid-pitch BGAs. For very fine pitch BGAs with very high pin counts, there is no choice but to use blind vias as part of the dogbone scallop to reach the internal layers, and will have to use higher layer counts in the HDI PCB stackup. This is due to limitations on the net count per layer, which applies even if the total pin count on fine-pitch devices is low.

GET PCB AND ASSEMBLY SERVICE QUOTE NOW!

For differential pairs, trace coupling also needs to be maintained underneath the BGA package. In protocols like PCIe or DDR using differential pairs, it’s easy to get to the outer two rows in the BGA directly on the top signal layer. For inner layers, microvias can be used with dogbone scallops, or microvias can be placed in pads to ensure adjacent traces remain coupled. When passing through plane layers in the HDI PCB stackup, always be sure to include the appropriate pad diameter. Also, try to mirror any bends on both traces of the differential pair to maintain symmetry and coupling. If you are using a coarse pitch package and very thin traces, you may be able to route a differential pair between the pads instead of having to put the trace pair between one pair of traces.

As with any other design, before creating an HDI PCB stackup or starting layout, you should contact the manufacturer to ensure that their DFM guidelines are followed. There are many PCB manufacturers that are highly focused on HDI PCB manufacturing and assembly, and they can accommodate very thin, very dense traces, which can accommodate very many layers. Doing this important work first saves manufacturing costs and ensures better yields.