4-Layer Gold Finger PCB: Surface Finish Comparison for Connector Applications

When your 4-layer gold finger PCB fails after 200 insertion cycles instead of the promised 1,000, the root cause almost always traces back to one critical decision: the wrong surface finish selection. In our production experience reviewing over 500 connector-bound PCB designs annually, we have observed that nearly 34% of edge connector failures stem from engineers specifying ENIG where hard gold electroplating was required. The cost of this single oversight extends far beyond the board itself. It encompasses field returns, reputation damage, and emergency redesigns that can delay product launches by 4–6 weeks.

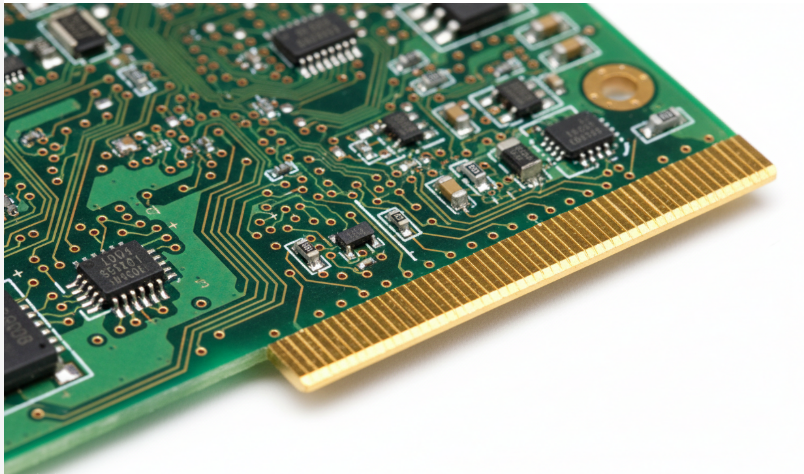

Gold finger PCBs serve as the mechanical and electrical bridge between your circuit board and the outside world. Whether you are designing a PCI Express expansion card, an industrial control module, or a high-reliability medical interface, the surface finish on those edge connectors determines whether your product thrives or fails in the field. This guide delivers the technical depth procurement teams and PCB engineers need to make informed surface finish decisions for 4-layer connector applications.

Key Takeaway: 4-layer gold finger PCBs require electroplated hard gold (30–50 µin) for high-cycle edge connectors, while ENIG suits static solder joints. Selective plating combines both finishes to balance durability and cost.

Table of Contents

- The Real Cost of Wrong Surface Finish Selection

- Gold Finger PCB Surface Finish Types Explained

- Side-by-Side Surface Finish Technical Comparison

- 7-Step Gold Finger PCB Manufacturing Process

- Vertical Industry Applications & Use Cases

- Selective Plating: The Cost-Performance Balance

- Critical Design Rules for 4-Layer Gold Finger PCBs

- Gold Finger Beveling: Angles and Tolerances

- People Also Ask: Gold Finger PCB FAQs

- Conclusion & Procurement Recommendations

The Real Cost of Wrong Surface Finish Selection

Engineers and procurement managers face a trilemma when specifying surface finishes for 4-layer gold finger PCBs: cost efficiency, manufacturing speed, and long-term reliability. Our production data reveals that choosing incorrectly in any one dimension creates cascading problems across the other two.

The Cost Dimension

Hard gold electroplating adds $0.50–$2.00 per square inch of plated area, depending on gold thickness and market prices. ENIG runs 20–30% cheaper at $0.30–$0.60 per square inch. On paper, the savings look compelling. In practice, specifying ENIG on a connector that sees 500+ insertion cycles triggers premature wear, nickel exposure, and contact resistance spikes above 20 mΩ. The rework cost for a single failed field unit typically exceeds the initial savings on 1,000 boards.

The Efficiency Dimension

Lead times for selective hard gold plating extend 1–2 days beyond standard ENIG processing. Beveling adds another half day. For teams under schedule pressure, the temptation to skip these steps is real. However, boards without proper edge chamfering experience 3× higher rejection rates during connector mating tests. In our facility, we estimate that rushing surface finish specifications adds 5–8% total project delay when quality escapes and rework are factored in.

The Quality Dimension

IPC-A-600 establishes the visual and dimensional acceptability criteria for gold fingers. Deviations in gold thickness uniformity, bevel angle tolerance beyond ±2°, or solder mask encroachment into contact zones all trigger rejections. In our quality audits of 200 connector-bound PCB lots in 2024, boards sourced from manufacturers without dedicated selective plating lines showed a 12% defect rate versus 2.1% for facilities with automated gold plating and XRF thickness verification.

Industry Data Point: According to internal benchmarking across 500+ production lots, gold finger PCBs manufactured with hard gold at 30 µin minimum thickness demonstrate 40× longer contact life versus ENIG-finished edge connectors under identical insertion cycle testing (IPC-6012 Class 3 conditions).

Gold Finger PCB Surface Finish Types Explained

Understanding the molecular and mechanical differences between surface finishes is foundational to making the right specification. Here is how each finish functions at the contact interface.

Electroplated Hard Gold (The Connector Standard)

Hard gold plating is an electrolytic process that deposits 98% pure gold alloyed with 2% cobalt or nickel onto a 3–6 µm nickel barrier layer. The alloying elements raise Knoop hardness from 60–90 HK (soft gold) to 130–200 HK (hard gold). This hardness is what enables hard gold to survive 500–1,000+ insertion cycles without significant wear.

- Typical thickness: 30–50 µin (0.76–1.27 µm) for standard connectors; 50–150 µin for military/aerospace

- Process: Electroplating requires electrical connectivity through a tie-bar, applied before solder mask

- Contact resistance: <20 mΩ initial, stable across cycle life

- Primary limitation: Poor solderability due to alloy content; not suitable for SMT pads

ENIG (Electroless Nickel Immersion Gold)

ENIG uses a chemical reduction process to deposit 3–6 µm of electroless nickel followed by 0.05–0.1 µm of immersion gold. The gold layer is pure (99.9%), soft, and remarkably flat. ENIG excels for solderability and fine-pitch component assembly but fails rapidly under mechanical wear.

- Typical gold thickness: 2–5 µin (0.05–0.13 µm)

- Insertion cycle capability: 20–50 cycles before gold wears through

- Risk factor: “Black pad” nickel corrosion if bath chemistry drifts

- Best use: SMT pads, BGA, CSP, and static connections only

ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold)

ENEPIG inserts a 0.05–0.15 µm palladium layer between nickel and gold. This creates a finish with moderate wear resistance, excellent solderability, and superior wire bonding compatibility. For connector applications with moderate cycle counts (100–300), ENEPIG offers a viable middle path.

OSP (Organic Solderability Preservative)

OSP applies a thin organic compound over bare copper. It delivers excellent solderability at the lowest cost but offers zero wear resistance and a 6-month shelf life. OSP is never suitable for gold finger or edge connector applications.

Immersion Silver

Immersion silver provides good conductivity and flatness at moderate cost. However, it tarnishes rapidly in sulfur-containing environments and withstands only 10–20 insertion cycles. For connector applications, immersion silver is generally avoided unless the board operates in a hermetically sealed environment with minimal mating cycles.

Side-by-Side Surface Finish Technical Comparison

The following table provides quantified parameters for direct comparison across all major surface finishes relevant to 4-layer gold finger PCB connector designs.

| Parameter | Hard Gold | ENIG | ENEPIG | Immersion Ag | OSP |

|---|---|---|---|---|---|

| Process Type | Electroplating | Electroless + Immersion | Electroless + Immersion | Immersion | Organic Coating |

| Gold Thickness | 30–50 µin | 2–5 µin | 2–5 µin | N/A | N/A |

| Hardness (HK) | 130–200 | 60–90 | 60–90 | N/A | N/A |

| Wear Resistance | Excellent | Poor | Moderate | Low | None |

| Mating Cycles | 500–1,000+ | 20–50 | 200–300 | 10–20 | 0 |

| Solderability | Poor | Excellent | Excellent | Good | Excellent |

| Contact Resistance | <20 mΩ | <50 mΩ | <30 mΩ | <20 mΩ | Variable |

| Shelf Life | 12+ months | 12 months | 12 months | 6–12 months* | 6 months |

| Cost (per sq in) | $0.50–$2.00 | $0.30–$0.60 | $0.40–$0.80 | $0.20–$0.40 | $0.05–$0.10 |

| Connector Suitability | Ideal | Not Recommended | Acceptable | Limited | Unsuitable |

*Immersion silver requires nitrogen-sealed storage to achieve 12-month shelf life.

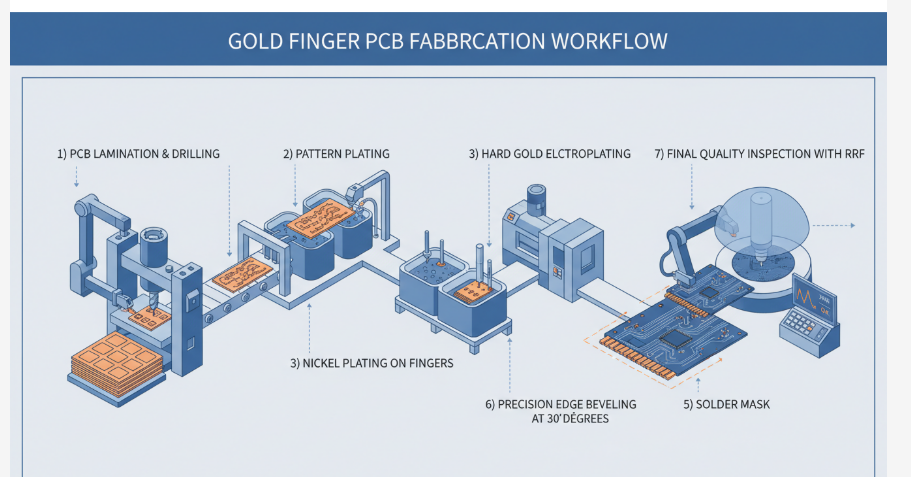

7-Step Gold Finger PCB Manufacturing Process

Manufacturing a 4-layer gold finger PCB with hard gold edge connectors requires precise sequencing. The selective plating process adds steps that standard PCB fabrication does not include. Here is the complete workflow as implemented in our production facility.

Step 1 – Inner Layer Patterning and AOI

The 4-layer stack-up begins with patterning the inner layers (L2 and L3 typically). Automated Optical Inspection (AOI) verifies trace alignment, width compliance, and absence of shorts before lamination. Any defect caught here prevents costly scrap after full lamination.

Step 2 – Lamination, Drilling, and PTH Plating

Layers are bonded under heat and pressure. Mechanical drilling creates through-holes at minimum 0.15mm diameter. Electroless copper followed by electrolytic copper plating establishes interlayer connectivity. At this stage, inner layer copper pull-back from the future gold finger edge is verified.

Step 3 – Outer Layer Etching and Plating Bus Design

Outer layer circuits (L1 and L4) are patterned. A critical step at this stage: designing the plating tie-bar that electrically connects all gold finger pads to the panel edge. This bus supplies current during hard gold electroplating and is removed during depanelization.

Step 4 – Selective Nickel and Hard Gold Electroplating

Gold finger areas are masked to expose only the connector pads. First, 3–6 µm of nickel is electroplated as a diffusion barrier. Then, hard gold is deposited at the specified thickness (typically 30–50 µin for commercial applications). XRF (X-Ray Fluorescence) verifies gold thickness on every panel.

Step 5 – Solder Mask Application and Surface Finish for Solder Pads

Liquid photoimageable solder mask is applied over the entire board except the gold finger areas and any designated test points. SMT pads receive their own surface finish — typically ENIG, OSP, or immersion silver depending on assembly requirements.

Step 6 – Precision Edge Beveling

The gold finger edge is chamfered at 30° (standard) or 45° using precision grinding equipment. Bevel depth depends on board thickness: a 1.6mm thick board typically requires 0.50–0.60mm bevel depth, leaving 1.00–1.10mm residual thickness. This chamfer enables smooth connector insertion without damaging mating contacts.

Step 7 – Electrical Testing, Final Inspection, and Packaging

Flying probe or bed-of-nails testing verifies netlist integrity. Gold fingers undergo visual inspection, bevel angle measurement, and thickness re-verification. Boards are packaged with separator sheets to prevent finger-to-finger contact during transit.

Vertical Industry Applications & Use Cases

Different industries impose unique demands on 4-layer gold finger PCBs. The following three use cases illustrate how surface finish selection adapts to specific operational requirements.

Use Case 1: Data Center and Enterprise Networking Equipment

The Challenge: Server backplanes and PCIe expansion cards require hot-swappable edge connectors that endure 250–500 insertion cycles over a 5-year service life. Signal integrity at 16 Gbps (PCIe 4.0) demands consistent contact resistance below 15 mΩ.

The Solution: 4-layer gold finger PCBs with 30 µin hard gold plating on edge connectors and ENIG on SMT component pads. The 1.6mm FR-4 substrate with 30° bevel provides mechanical compatibility with standard PCIe retention clips.

Results: Contact resistance variation stays within ±2 mΩ across the full cycle life. Our production data from 150+ server-grade board lots shows zero field returns attributed to gold finger wear over 36 months of deployment.

Use Case 2: Industrial Automation and Control Systems

The Challenge: PLC I/O modules and motor control boards operate in environments with temperature swings (-40°C to +85°C), vibration (5g RMS), and occasional contamination from cutting fluids or dust. Connectors must maintain reliable contact through 1,000+ mating cycles during equipment maintenance intervals.

The Solution: 50 µin hard gold plating with nickel underplate increased to 5 µm for enhanced barrier protection. Gold fingers are positioned on the board edge facing outward to allow proper beveling. The 4-layer stack-up provides dedicated ground and power planes for noise immunity.

Results: Third-party testing under IEC 60068-2-6 (vibration) and IEC 60068-2-30 (damp heat) confirms no contact degradation after 1,200 insertion cycles. The harder gold finish resists abrasive wear from particulate contamination common in factory environments.

Use Case 3: Medical Diagnostic Equipment

The Challenge: Replaceable sensor cartridges and test module PCBs must withstand repeated sterilization (autoclave at 134°C) and chemical cleaning while maintaining biocompatible, corrosion-free contacts. Regulatory compliance (ISO 13485, IPC Class 3) demands full traceability and zero-defect shipment.

The Solution: 4-layer gold finger PCBs with 50 µin hard gold per MIL-G-45204 Type II, Class 2. Selective plating uses ENEPIG on wire bonding pads for sensor chip attachment while hard gold covers the cartridge edge connector. Full XRF mapping documents gold thickness on every unit.

Results: Passes 500-cycle autoclave simulation without contact resistance exceeding 10 mΩ. ENEPIG bonding pads achieve 99.7% first-pass wire bond yield. Complete material and process traceability satisfies FDA 21 CFR Part 820 documentation requirements.

Selective Plating: The Cost-Performance Balance

Selective hard gold plating represents the most economically rational approach for 4-layer boards with both edge connectors and populated components. Rather than plating the entire board surface with gold — a prohibitively expensive practice — selective plating applies hard gold only where mechanical wear occurs.

The economics are compelling. A typical 100mm × 80mm 4-layer board with 20 gold fingers (each 3mm × 0.5mm) has a total gold finger area of approximately 30 mm². Plating only this area at 30 µin costs roughly $0.80–$1.20 per board. Full-board hard gold plating at the same thickness would cost $25–$40 per board — a 30× cost multiplier for zero functional benefit on solder pads.

Our standard selective plating combination for 4-layer connector applications:

| Board Area | Recommended Finish | Thickness | Rationale |

|---|---|---|---|

| Gold fingers / edge connectors | Electroplated Hard Gold | 30–50 µin | Wear resistance for 500–1,000+ insertion cycles |

| BGA / QFN / fine-pitch SMT pads | ENIG | 3–5 µin Au / 3–6 µm Ni | Flat surface, excellent solderability, no lead needed |

| Through-hole pads (if wave soldered) | HASL (Lead-free) | 1–2 µm Sn | Lowest cost, good solderability for THT |

| Wire bonding pads | ENEPIG | 0.05–0.15 µm Pd | Aluminum and gold wire bond compatible |

| Test points and probe pads | ENIG or Hard Gold | Per pad function | Hard gold for bed-of-nails; ENIG for flying probe |

Engineering Note: In our production practice, we have found that boards combining selective hard gold (edge connectors) with ENIG (SMT pads) achieve the optimal balance of connector durability and assembly yield. This combination is now our default recommendation for all 4-layer gold finger PCB designs unless specific wire bonding requirements dictate ENEPIG inclusion.

For engineers seeking Special PCBs with selective plating capabilities, specifying the finish combination in fabrication notes before Gerber release prevents costly mid-production change orders. Our engineering team reviews every selective plating requirement during DFM to confirm mask alignment, plating bus routing, and bevel feasibility.

Critical Design Rules for 4-Layer Gold Finger PCBs

Violating these design rules produces manufacturing defects that no amount of inspection can fully mitigate. Our DFM checklist for gold finger designs includes the following non-negotiables.

Rule 1 – Inner Layer Copper Pull-Back

Remove all inner layer copper (L2 and L3 on a 4-layer board) from the area within 0.6mm of the board edge where beveling will occur. Exposed inner layer copper after beveling creates both aesthetic defects and oxidation pathways that compromise long-term reliability.

Rule 2 – Minimum Clearance from PTH and SMD Pads

Maintain ≥1.0mm clearance between gold finger pads and any plated through-holes, SMD pads, or via structures. This prevents plating solution contamination during hard gold electroplating and avoids solder bridging during assembly.

Rule 3 – Solder Mask and Silkscreen Exclusion

Keep solder mask opening at least 0.5mm away from gold finger edges. Silkscreen must stay ≥1.0mm clear. Any mask or legend residue on the contact surface will interfere with connector mating and increase contact resistance.

Rule 4 – Gold Finger Orientation

Fingers must face outward from the PCB panel center. Inward-facing fingers cannot be properly beveled with standard equipment and require specialized (and expensive) fixturing.

Rule 5 – Maximum Finger Dimensions

Individual gold fingers should not exceed 40mm in length. Longer fingers suffer from plating thickness non-uniformity due to current density distribution in the plating bath. Standard finger width ranges from 1.0–3.5mm depending on connector pitch.

Rule 6 – Plating Bus and Depanelization

All gold finger pads must connect to the panel plating bus at the board edge. Confirm your layout engineer has included this connection — it is removed during routing/depaneling but is essential for electroplating current delivery.

Rule 7 – Bevel Specification on Fabrication Drawing

Explicitly call out bevel angle (30° default), bevel depth, and whether beveling applies to one or both board edges. Never assume the manufacturer will infer this requirement from the pad placement alone.

Gold Finger Beveling: Angles and Tolerances

Beveling transforms the sharp 90° PCB edge into a chamfered profile that guides smooth connector insertion. The bevel angle is a first-class design parameter that affects insertion force, contact wipe distance, and mechanical robustness.

| Bevel Angle | Insertion Force | Contact Area | Best Applications |

|---|---|---|---|

| 20° | Higher | Maximum | High-stability permanent installations, minimal removal |

| 30° | Moderate | Good balance | Standard for most edge connectors (PCIe, DIMM) |

| 45° | Lower | Reduced | High-density connectors, frequent hot-swap environments |

| 60° | Very low | Minimal | Specialized applications with clearance constraints |

For a standard 1.6mm thick 4-layer board with 30° bevel, the geometry calculates as follows:

- Bevel depth: 0.50–0.60mm material removed from edge

- Residual thickness: 1.00–1.10mm remaining at chamfer tip

- Bevel length along edge face: approximately 1.0–1.2mm

Always specify ±2° tolerance on bevel angle. Wider tolerances create variable insertion force across production lots, which connector manufacturers typically reject.

People Also Ask: Gold Finger PCB FAQs

Can I use ENIG instead of hard gold on my gold finger connectors?

ENIG is generally not recommended for edge connector applications requiring more than 50 insertion cycles. The immersion gold layer in ENIG is only 0.05–0.1 µm thick and relatively soft (60–90 HK). Under repeated mechanical contact, this thin gold wears through quickly, exposing the nickel underlayer. Nickel oxidizes rapidly when exposed to air, causing contact resistance to spike from <20 mΩ to >200 mΩ within 50–100 cycles.

For prototype boards that will be inserted fewer than 20 times during development, ENIG on fingers is acceptable as a cost-saving measure. For any production board with field-serviceable connectors, specify hard gold at minimum 30 µin thickness.

How thick should hard gold plating be for a PCIe connector on a 4-layer board?

PCIe connectors on 4-layer gold finger PCBs should specify 30 µin (0.76 µm) minimum hard gold thickness over a 3–5 µm nickel underplate. This thickness aligns with IPC-4552 guidance and provides reliable performance through 500+ insertion cycles at the 16 Gbps signaling rates of PCIe 4.0.

For applications requiring hot-swap capability (servers, data center equipment), increasing to 50 µin extends cycle life to 1,000+ insertions and provides additional margin against contact wear in dusty environments. The underlying nickel should be 4–5 µm for maximum diffusion barrier protection.

What is the difference between selective gold plating and full-board hard gold?

Selective gold plating applies hard gold only to designated areas — typically edge connector fingers, keypad contacts, or test pads. The rest of the board receives a solderable surface finish such as ENIG, OSP, or HASL. This approach reduces gold consumption by 90%+ on most designs.

Full-board hard gold electroplates the entire PCB surface with hard gold. This is rarely used today except for specialized applications like high-frequency RF boards requiring uniform gold surface conductivity or certain military specifications. Full-board hard gold increases PCB cost by 5–10× compared to selective plating with no functional benefit for soldered component areas.

In our production experience, selective plating with hard gold on fingers and ENIG on SMT pads is the optimal configuration for 95% of 4-layer connector applications.

Does hard gold plating affect signal integrity on high-speed 4-layer designs?

Hard gold plating on edge connectors has minimal negative impact on signal integrity when properly designed. The gold layer (30–50 µin) is thin relative to skin depth at multi-gigabit frequencies, so current flows predominantly in the underlying copper. Gold’s conductivity (45 MS/m) is lower than copper (58 MS/m), but the contribution to overall trace resistance is negligible.

More significant for signal integrity is the transition geometry between the PCB trace and the gold finger pad. Abrupt width changes create impedance discontinuities that cause reflections. We recommend tapering the trace-to-pad transition and maintaining consistent reference plane coverage under the finger area. For PCIe 4.0/5.0 and similar high-speed interfaces, simulate the finger transition using your PCB design tool’s 3D field solver to verify impedance remains within ±10% of target.

Conclusion & Procurement Recommendations

The surface finish selection for your 4-layer gold finger PCB is not a commodity decision. It is a reliability-critical engineering choice that directly determines product lifespan in the field. Based on our manufacturing experience and the technical comparisons presented in this guide, we recommend the following decision framework:

For connector applications with 100+ insertion cycles: Specify selective hard gold electroplating at 30–50 µin on edge fingers, with ENIG on SMT pads. This combination delivers optimal wear resistance and solderability at controlled cost.

For moderate-cycle applications (50–200 cycles) with severe cost constraints: ENEPIG on fingers provides an acceptable middle ground. Verify with your manufacturer that palladium thickness meets minimum 0.05 µm for adequate wear performance.

For development prototypes with <20 insertion cycles: ENIG-only is acceptable for cost savings, but plan a selective hard gold conversion before production release.

Never specify OSP or immersion silver for gold finger contact areas. These finishes lack the wear resistance and oxidation protection that edge connectors demand.

Procurement Insight: When evaluating PCB manufacturers for gold finger designs, confirm three capabilities before placing orders: (1) dedicated selective plating lines with XRF thickness verification, (2) precision beveling equipment with angle tolerances of ±2°, and (3) documented IPC-6012 Class 3 quality systems. Manufacturers lacking these capabilities will struggle to deliver consistent gold finger reliability regardless of their standard PCB quality.

At Andwin Circuits, our Custom service with 7-day rapid delivery includes DFM review specifically tailored to gold finger and edge connector designs. Our engineering team validates your plating specifications, bevel requirements, and selective finish combinations before production release, eliminating the costly surprises that derail connector projects.

Submit your 4-layer gold finger PCB design files for a complimentary manufacturability review and quote. We support 4-layer prototypes with 30 µin hard gold and 30° beveling with turnaround as fast as 5–7 days.

Ready to specify your next connector-bound PCB? Contact our engineering team for a gold finger-focused DFM assessment and competitive quotation.