Demystifying vias in high-speed pcb design

Understanding The Role Of Vias In High-Speed PCB Design

In the realm of high-speed printed circuit board (PCB) design, understanding the role of vias is crucial for ensuring optimal performance and reliability. Vias, which are small conductive pathways that connect different layers of a PCB, play a pivotal role in the electrical and mechanical integrity of the board. As electronic devices become increasingly complex and compact, the demand for high-speed data transmission has surged, making the design of PCBs more challenging. Consequently, the role of vias in high-speed PCB design has garnered significant attention from engineers and designers alike.

To begin with, it is essential to comprehend the basic function of vias.

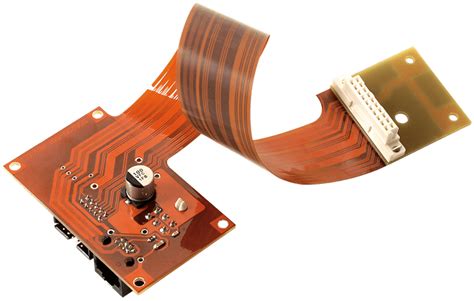

Vias serve as vertical interconnections between the various layers of a PCB, allowing signals and power to traverse the board efficiently. They are typically categorized into three types: through-hole vias, blind vias, and buried vias. Through-hole vias extend from the top to the bottom layer of the PCB, while blind vias connect an outer layer to one or more inner layers without passing through the entire board. Buried vias, on the other hand, are located entirely within the inner layers, invisible from the surface. Each type of via has its own set of advantages and limitations, which must be carefully considered during the design process.

In high-speed PCB design, the role of vias becomes even more critical due to their impact on signal integrity.

As signal frequencies increase, the parasitic inductance and capacitance associated with vias can lead to signal degradation, reflection, and crosstalk. These issues can significantly affect the performance of high-speed circuits, leading to data errors and reduced system reliability. Therefore, it is imperative to minimize the adverse effects of vias by employing strategic design techniques.

One effective approach to mitigating via-related issues is to optimize the via geometry.

By reducing the via stub length, which is the portion of the via that extends beyond the signal layer, designers can minimize signal reflections and improve signal integrity. Additionally, using smaller via diameters and annular rings can help reduce parasitic capacitance and inductance. Another technique involves the use of back-drilling, a process that removes the unused portion of the via, further reducing the stub length and enhancing signal performance.

Moreover, the placement of vias plays a significant role in high-speed PCB design.

Proper via placement can help minimize crosstalk and electromagnetic interference (EMI) between adjacent signal traces. Designers often employ via stitching, a technique that involves placing multiple vias around a signal trace to create a low-impedance return path, thereby reducing EMI and improving signal integrity. Furthermore, careful consideration of via placement in relation to power and ground planes can help maintain a stable power distribution network, which is essential for high-speed applications.

In conclusion, understanding the role of vias in high-speed PCB design is paramount for achieving optimal performance and reliability. By carefully considering via types, geometry, and placement, designers can effectively mitigate the adverse effects of vias on signal integrity and EMI. As technology continues to advance and the demand for high-speed data transmission grows, the importance of mastering via design in PCB development will only become more pronounced. Through continued research and innovation, engineers can unlock new possibilities in high-speed electronics, paving the way for the next generation of advanced devices.

Techniques For Optimizing Via Placement In High-Speed Circuits

In the realm of high-speed printed circuit board (PCB) design, the strategic placement of vias is a critical factor that can significantly influence the performance and reliability of electronic circuits. Vias, which are essentially conductive pathways that allow signals to traverse different layers of a PCB, play a pivotal role in the overall signal integrity and electromagnetic compatibility of high-speed circuits. As the demand for faster and more efficient electronic devices continues to grow, understanding the techniques for optimizing via placement becomes increasingly important for engineers and designers.

To begin with, it is essential to recognize that vias introduce discontinuities in the signal path,

which can lead to signal reflection, impedance mismatch, and increased electromagnetic interference (EMI). Therefore, minimizing these adverse effects is a primary objective when placing vias in high-speed circuits. One effective technique is to carefully consider the via stub length. Via stubs, which are the unused portions of a via that extend beyond the signal layer, can act as resonant structures that degrade signal quality. By employing back-drilling or controlled-depth drilling, designers can remove these stubs, thereby reducing their impact on signal integrity.

Moreover, the placement of vias in relation to other components and traces is another crucial aspect.

Ensuring that vias are placed symmetrically and in close proximity to the components they connect can help maintain a consistent impedance profile, which is vital for high-speed signal transmission. Additionally, when routing differential pairs, it is advisable to use vias in pairs to maintain the symmetry and balance of the differential signals. This practice helps in minimizing skew and preserving the integrity of the differential signaling.

Transitioning to another important consideration, the use of via stitching and via fences can be instrumental in enhancing the performance of high-speed circuits

. Via stitching involves placing multiple vias around a signal trace or plane to provide a low-inductance return path for high-frequency signals. This technique is particularly beneficial in reducing EMI and improving signal integrity by ensuring that the return current path is as short and direct as possible. Similarly, via fences, which are rows of vias placed along the edges of a PCB, can serve as effective barriers to contain electromagnetic fields and prevent them from radiating into adjacent areas.

Furthermore, the choice of via type can also impact the optimization process.

Designers can choose from through-hole vias, blind vias, and buried vias, each offering distinct advantages and trade-offs. Through-hole vias are the most common and cost-effective, but they can introduce more parasitic inductance and capacitance. On the other hand, blind and buried vias, which do not extend through the entire board, can help reduce these parasitic effects and are often preferred in high-density and high-speed applications.

In conclusion, optimizing via placement in high-speed PCB design is a multifaceted challenge that requires a comprehensive understanding of the interplay between signal integrity, EMI, and manufacturing constraints. By employing techniques such as minimizing via stub lengths, ensuring symmetrical placement, utilizing via stitching and fences, and selecting appropriate via types, designers can significantly enhance the performance and reliability of high-speed circuits. As technology continues to advance, the importance of mastering these techniques will only grow, underscoring the need for ongoing education and adaptation in the field of PCB design.

Impact Of Via Types On Signal Integrity In High-Speed PCBs

In the realm of high-speed printed circuit board (PCB) design, the role of vias is often underestimated, yet their impact on signal integrity is profound. Vias, which are essentially conductive pathways that allow signals to traverse different layers of a PCB, are crucial in maintaining the performance and reliability of high-speed circuits. As the demand for faster and more efficient electronic devices grows, understanding the influence of various via types on signal integrity becomes increasingly important.

To begin with, it is essential to recognize that vias introduce discontinuities in the signal path, which can lead to reflections, impedance mismatches, and signal degradation.

These issues are particularly pronounced in high-speed applications where even minor disruptions can significantly affect performance. The choice of via type, therefore, plays a pivotal role in mitigating these adverse effects. Through-hole vias, for instance, are the most traditional type, extending through the entire thickness of the PCB. While they are robust and easy to manufacture, they can introduce significant parasitic inductance and capacitance, which can degrade signal integrity at high frequencies.

In contrast, blind and buried vias offer a more sophisticated solution by connecting only specific layers of the PCB.

Blind vias connect an outer layer to one or more inner layers, while buried vias connect only inner layers without reaching the outer surfaces. These via types reduce the parasitic effects associated with through-hole vias, thereby enhancing signal integrity. However, they also increase manufacturing complexity and cost, necessitating a careful balance between performance and budget considerations.

Moreover, microvias, which are smaller in diameter and typically used in high-density interconnect (HDI) PCBs, provide another avenue for improving signal integrity.

Their reduced size minimizes parasitic inductance and capacitance, making them ideal for high-speed applications. Additionally, microvias enable more compact and efficient designs by allowing for greater routing density. Despite these advantages, the use of microvias requires advanced manufacturing techniques and can lead to increased production costs.

Transitioning from the types of vias to their placement and design, it is crucial to consider how these factors influence signal integrity.

The placement of vias should be strategically planned to minimize signal path length and avoid unnecessary detours, which can introduce additional delay and distortion. Furthermore, the aspect ratio of vias, defined as the ratio of the via’s length to its diameter, should be optimized to reduce impedance discontinuities. A lower aspect ratio generally results in better signal integrity, as it reduces the via’s inductive and capacitive effects.

Additionally, the use of via stitching and via shielding techniques can further enhance signal integrity.

Via stitching involves placing multiple vias around a signal via to provide a return path for high-frequency currents, thereby reducing electromagnetic interference (EMI) and crosstalk. Similarly, via shielding involves surrounding a signal via with ground vias to isolate it from other signals, enhancing signal integrity by minimizing interference.

In conclusion, the impact of via types on signal integrity in high-speed PCB design is a multifaceted issue that requires careful consideration of various factors. By understanding the characteristics and implications of different via types, as well as optimizing their placement and design, engineers can significantly improve the performance and reliability of high-speed electronic devices. As technology continues to advance, the importance of mastering via design in high-speed PCBs will only grow, underscoring the need for ongoing research and innovation in this critical area.

Best Practices For Via Design In High-Speed PCB Applications

In the realm of high-speed printed circuit board (PCB) design, the role of vias is often underestimated, yet they are crucial components that significantly influence the performance and reliability of the final product. Vias, which are essentially conductive pathways that allow signals to traverse between different layers of a PCB, can introduce various challenges if not designed properly. Therefore, understanding best practices for via design in high-speed applications is essential for engineers aiming to optimize signal integrity and minimize potential issues.

To begin with, it is important to recognize that vias can introduce parasitic inductance and capacitance, which can adversely affect signal integrity, especially in high-speed applications

. These parasitic elements can cause signal reflections, crosstalk, and impedance mismatches, leading to degraded performance. Consequently, one of the best practices is to minimize via inductance by reducing the via stub length. A via stub is the portion of the via that extends beyond the signal layer it connects to, and it can act as an unwanted antenna, picking up noise and causing signal degradation. By employing techniques such as back-drilling, which removes the unused portion of the via, designers can effectively reduce stub length and its associated parasitic effects.

Moreover, the choice of via type plays a significant role in high-speed PCB design.

While through-hole vias are commonly used, blind and buried vias offer advantages in high-speed applications by reducing the number of layers a signal must traverse, thereby minimizing signal path length and associated parasitics. Blind vias connect an outer layer to one or more inner layers without passing through the entire board, while buried vias connect only inner layers. These types of vias can help maintain signal integrity by reducing the number of transitions a signal must make, which is particularly beneficial in densely packed, multi-layer boards.

In addition to selecting the appropriate via type, careful consideration of via placement is crucial.

Vias should be strategically placed to minimize their impact on signal paths. For instance, placing vias too close to each other can lead to crosstalk, where signals in adjacent vias interfere with one another. To mitigate this, maintaining adequate spacing between vias is recommended. Furthermore, when routing high-speed signals, it is advisable to avoid placing vias in critical signal paths whenever possible. If a via is necessary, ensuring that it is placed symmetrically and that the return path is uninterrupted can help preserve signal integrity.

Another best practice involves the use of via stitching, which entails placing multiple vias around a signal via to provide a low-inductance return path for high-frequency signals.

This technique is particularly useful in reducing electromagnetic interference (EMI) and improving the overall performance of the PCB. Via stitching can also enhance thermal management by providing additional paths for heat dissipation, which is an added benefit in high-power applications.

Finally, simulation and modeling tools are invaluable in the via design process.

These tools allow designers to predict the electrical behavior of vias and assess their impact on the overall PCB performance. By simulating different via configurations and analyzing their effects on signal integrity, designers can make informed decisions and optimize their designs accordingly.

In conclusion, while vias are small components within a PCB, their impact on high-speed applications is significant. By adhering to best practices such as minimizing via stub length, selecting appropriate via types, strategically placing vias, employing via stitching, and utilizing simulation tools, designers can effectively manage the challenges associated with vias and ensure optimal performance in high-speed PCB designs.