How to Solve Impedance Discontinuity in PCB Design

Introduction

Impedance control is a critical aspect of high-speed PCB design, ensuring signal integrity and minimizing reflections, crosstalk, and electromagnetic interference (EMI). However, impedance discontinuities—sudden changes in characteristic impedance along a transmission line—can degrade signal quality, leading to data errors and system failures.

This article explores the causes of impedance discontinuities in PCB design, their impact on signal integrity, and effective strategies to mitigate them.

1. Understanding Impedance Discontinuity

Impedance discontinuity occurs when the characteristic impedance of a transmission line changes abruptly due to variations in trace geometry, material properties, or routing conditions. Common causes include:

- Trace Width Variations: Changes in trace width alter impedance.

- Layer Transitions: Moving signals between layers with different dielectric constants.

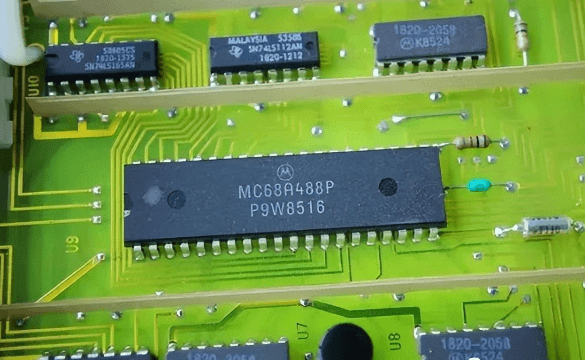

- Vias and Connectors: Parasitic capacitance and inductance from vias and connectors.

- Bends and Corners: Sharp angles in traces causing impedance mismatches.

- Component Pads and Stubs: Large pads or unterminated stubs introducing capacitance.

When impedance mismatches occur, signal reflections arise, leading to:

- Signal distortion (ringing, overshoot, undershoot)

- Increased bit error rates (BER)

- Reduced timing margins

- EMI radiation

2. Common Causes of Impedance Discontinuity

2.1 Trace Width and Spacing Variations

- Problem: Traces that narrow or widen abruptly (e.g., near connectors or IC pads) cause impedance changes.

- Solution: Maintain consistent trace width and spacing. Use tapered transitions if width changes are unavoidable.

2.2 Layer Transitions

- Problem: Moving signals between layers with different dielectric constants (Dk) or thicknesses alters impedance.

- Solution:

- Use symmetrical stack-ups to maintain consistent impedance.

- Minimize layer transitions; if necessary, use back-drilled or blind vias to reduce stub effects.

2.3 Vias and Through-Holes

- Problem: Vias introduce parasitic capacitance and inductance, disrupting impedance.

- Solution:

- Use smaller via diameters and antipads to reduce capacitance.

- Implement via stitching or ground return vias for high-speed signals.

- Consider microvias or buried vias for dense designs.

2.4 Sharp Bends and Corners

- Problem: 90-degree bends increase capacitance, causing impedance drops.

- Solution: Use 45-degree bends or curved traces to maintain smooth impedance.

2.5 Component Pads and Stubs

- Problem: Large pads (e.g., BGA, connectors) introduce capacitive loading.

- Solution:

- Use smaller pads where possible.

- Route signals away from stubs or use termination techniques.

3. Techniques to Minimize Impedance Discontinuity

3.1 Controlled Impedance Routing

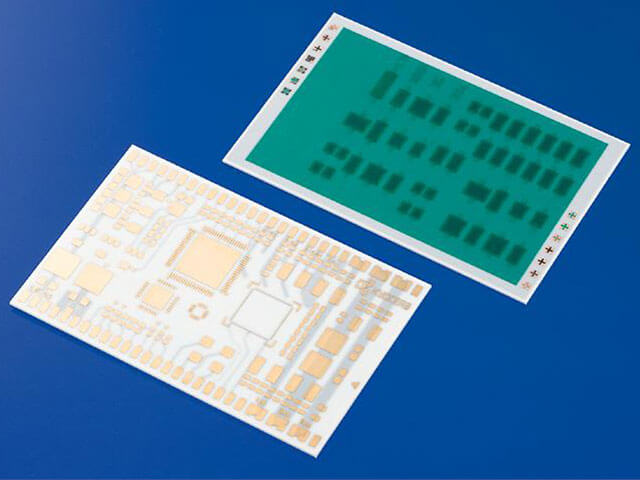

- Use PCB stack-up calculators to determine trace width, spacing, and dielectric thickness for target impedance (e.g., 50Ω, 100Ω differential).

- Work with manufacturers to ensure dielectric materials (e.g., FR4, Rogers) meet specifications.

3.2 Proper Via Design

- Back-Drilling: Removes unused via stubs to reduce reflections.

- Differential Via Pairing: Ensures balanced impedance for differential signals.

- Via Shielding: Surround signal vias with ground vias to minimize crosstalk.

3.3 Smooth Transitions

- Tapered Traces: Gradually change trace width to minimize reflections.

- Mitered Corners: Replace sharp angles with 45-degree bends.

3.4 Termination Techniques

- Series Termination: Adds a resistor near the driver to match impedance.

- Parallel Termination: Places a resistor at the receiver end to absorb reflections.

- AC Termination: Uses an RC network to reduce high-frequency ringing.

3.5 Simulation and Validation

- Use SPICE, HyperLynx, or ADS to simulate impedance and identify discontinuities.

- Perform Time-Domain Reflectometry (TDR) testing to measure actual impedance.

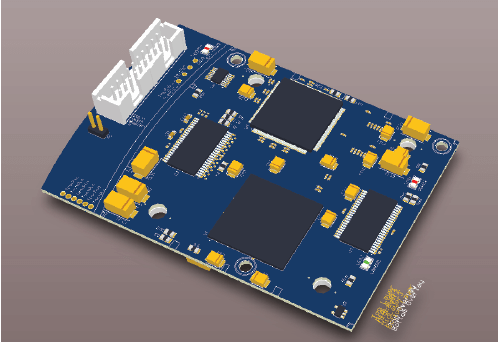

4. Advanced PCB Design Strategies

4.1 Embedded Passive Components

- Integrate resistors and capacitors into the PCB to reduce discontinuities from discrete components.

4.2 Coplanar Waveguide Design

- Uses grounded copper alongside traces to maintain consistent impedance, especially in RF designs.

4.3 High-Speed Material Selection

- Low-loss dielectrics (e.g., Rogers, Isola) provide better impedance control than standard FR4.

4.4 3D Electromagnetic Simulation

- Tools like CST Studio Suite or HFSS analyze complex structures (e.g., vias, connectors) for impedance effects.

5. Case Study: Fixing Impedance Discontinuity in a DDR4 Interface

Problem: A DDR4 memory interface exhibited signal integrity issues due to impedance mismatches at via transitions.

Solution:

- Redesigned Vias: Used smaller laser-drilled microvias with optimized antipads.

- Added Ground Return Vias: Placed ground vias adjacent to signal vias to reduce inductance.

- Simulated with TDR: Verified impedance consistency before fabrication.

Result: Signal reflections reduced by 60%, improving eye diagram margins.

6. Conclusion

Impedance discontinuities are inevitable in PCB design but can be managed with careful planning and simulation. Key takeaways:

- Maintain consistent trace geometry and layer stack-up.

- Optimize via design to minimize parasitic effects.

- Use termination techniques to reduce reflections.

- Validate designs with simulation and TDR testing.

By applying these techniques, designers can achieve robust high-speed PCB layouts with minimal signal degradation.