How to Properly Layout a 40A Power Supply: Copper Pour, Vias, and Current Loops

Introduction

Designing printed circuit boards (PCBs) for high-current applications like 40A power supplies requires careful consideration of several critical factors. Unlike low-power circuits where layout may be more forgiving, high-current designs demand precise attention to copper weight, via placement, thermal management, and current loop minimization. This 2000-word guide will explore best practices for laying out 40A power circuits, focusing on three key aspects: copper pour strategies, via implementation, and current loop control.

Understanding the Challenges of 40A Current

Before diving into layout techniques, it’s essential to understand why 40A presents unique challenges:

- Resistance Concerns: Even small resistances can lead to significant power loss (P=I²R). For example, just 1mΩ of resistance at 40A creates 1.6W of heat.

- Thermal Management: High currents generate substantial heat that must be dissipated properly.

- Voltage Drop: Excessive voltage drop along traces can affect circuit performance.

- Electromagnetic Interference (EMI): High current switching creates strong magnetic fields that can interfere with nearby circuits.

Section 1: Copper Pour Strategies for 40A Currents

1.1 Copper Weight Selection

For 40A currents, standard 1oz (35μm) copper is generally insufficient. Consider:

- 2oz (70μm) Copper: Minimum recommendation for 40A designs

- 3oz (105μm) Copper: Better for reduced voltage drop and thermal performance

- 4oz (140μm) Copper: Ideal for highest efficiency and thermal management

Calculation example: A 100mm long, 10mm wide 2oz trace has approximately 0.83mΩ resistance, resulting in 33mV drop at 40A (V=IR).

1.2 Trace Width Considerations

While standard calculators provide starting points, high-current designs require additional considerations:

- Temperature Rise: Aim for <20°C temperature rise in normal operation

- Current Density: Keep below ~500A/cm² for reliable long-term operation

- Practical Widths: For 2oz copper, 10-15mm widths are typical for 40A

Use the modified IPC-2152 formula for high-current traces:

Width = (I / (k * ΔT^0.44))^(1/0.725)Where:

- I = current (A)

- ΔT = temperature rise (°C)

- k = 0.048 for outer layers, 0.024 for inner layers

1.3 Copper Pour Shapes and Routing

- Avoid Sharp Corners: Use 45° angles or rounded corners to prevent current crowding

- Tapered Transitions: When changing widths, use gradual tapers (length ≥ 3× width change)

- Branching Strategies: For splitting current, use symmetrical “Y” branches rather than “T” junctions

1.4 Multi-Layer Current Distribution

When using multiple layers for current carrying:

- Mirror Layouts: Place identical current paths directly above/below each other

- Interleaved Phases: For multi-phase designs, alternate phase layers to cancel magnetic fields

- Current Sharing: Ensure parallel paths have equal lengths and impedances

Section 2: Via Implementation for High Current

2.1 Via Current Capacity

Standard vias are inadequate for 40A. Key parameters:

- Via Diameter: Use ≥0.5mm finished hole size (preferably 0.8-1.0mm)

- Annular Ring: Minimum 0.2mm additional beyond hole size

- Plating Thickness: Specify ≥25μm (1mil) copper plating

Current capacity estimation:

I = k * (ΔT^0.54) * (A^0.72)Where:

- I = current (A)

- ΔT = temperature rise (°C)

- A = via cross-sectional area (cm²)

- k = 5.2 for plating thickness ≥25μm

2.2 Via Arrays and Patterns

Single vias cannot handle 40A – use arrays:

- Uniform Distribution: Space vias evenly along current path

- Staggered Patterns: Alternate via positions in adjacent rows

- Minimum Spacing: Keep ≥2× via diameter center-to-center

Example via array for 40A:

- 10 vias of 0.8mm diameter, arranged in 2 rows of 5

- Provides ~4A per via with safety margin

2.3 Thermal Vias

For heat dissipation to inner layers or heatsinks:

- High Density Arrays: Place under power components

- Connection to Ground Planes: Use for additional thermal mass

- Fill Material: Consider thermally conductive via fill (copper or epoxy)

2.4 Via Placement Guidelines

- Current Entry/Exit Points: Place via arrays at component pads

- Layer Transitions: Use via arrays where current changes layers

- Avoid Current Bottlenecks: Ensure via arrays don’t create localized high-resistance points

Section 3: Managing Current Loops

3.1 Understanding Current Loops

Current loops in power circuits:

- Create varying magnetic fields

- Generate EMI

- Can induce noise in sensitive circuits

- Increase parasitic inductance

3.2 Minimizing Loop Area

Key strategies:

- Tight Component Placement: Keep power components close together

- Parallel Return Paths: Route supply and return paths adjacent to each other

- Layer Stackup Planning: Place supply and return layers adjacent

Loop area calculation:

A = I * d * μ₀ / (2π * B)Where:

- A = loop area (m²)

- I = current (A)

- d = distance between conductors (m)

- μ₀ = permeability of free space

- B = acceptable magnetic field strength

3.3 Multi-Layer Loop Control

For 4+ layer boards:

- Sandwich Technique: Place power between two ground planes

- Image Planes: Use adjacent reference planes for return current

- Decoupling Placement: Position decoupling capacitors to minimize high-frequency loops

3.4 High di/dt Considerations

For switching power circuits:

- Local Energy Storage: Place bulk capacitance near switches

- Gate Drive Loops: Keep gate drive loops small and away from power loops

- Shielding: Use grounded copper between sensitive and noisy areas

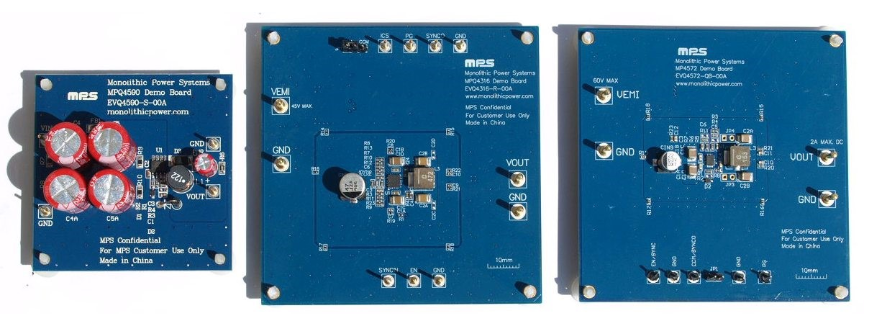

Practical Implementation Example

Step-by-Step 40A Buck Converter Layout

- Component Placement:

- Place input capacitors closest to switching FETs

- Position inductor for minimal AC current path

- Group output capacitors near load

- Copper Pour Implementation:

- 3oz outer layers, 2oz inner layers

- 12mm main power traces

- Gradual tapers at width changes

- Via Arrays:

- 8× 0.8mm vias at each switch node

- 6× 0.8mm vias at input/output connections

- Thermal via array under control IC

- Loop Control:

- Input cap to FET distance <5mm

- FET to inductor distance <8mm

- Return paths mirrored directly beneath supply paths

Thermal Considerations

Heat Dissipation Techniques

- Exposed Pads: Use large component pads for heatsinking

- Copper Area: Maximize unused board area for thermal relief

- Board Thickness: 2mm or thicker for better heat spreading

- External Heatsinks: Plan for mounting points if needed

Temperature Rise Estimation

Use the following approximation for copper areas:

ΔT ≈ P * RθWhere:

- P = power dissipated (W)

- Rθ = thermal resistance (°C/W)

For a 10cm² 2oz copper area:

Rθ ≈ 20°C/W (still air)

Verification and Testing

Design Verification Steps

- DC Resistance Measurement:

- Calculate expected resistance

- Verify with 4-wire measurement if possible

- Thermal Imaging:

- Identify hot spots under load

- Verify even current distribution

- Voltage Drop Testing:

- Measure at critical points under full load

- Compare with calculations

Simulation Tools

- DC Analysis: Verify voltage drops and current distribution

- Thermal Simulation: Predict temperature rises

- EMI Simulation: Analyze magnetic field emissions

Conclusion

Proper layout of 40A power circuits requires a holistic approach considering electrical, thermal, and electromagnetic factors. By implementing appropriate copper weights, strategic via arrays, and careful loop area control, designers can create reliable, efficient high-current PCBs. Always remember to:

- Use sufficient copper weight and width for current requirements

- Distribute current through multiple parallel vias

- Minimize all current loop areas, especially high di/dt paths

- Verify designs through calculation and measurement

Following these guidelines will help ensure your 40A power supply design meets performance requirements while remaining reliable and manufacturable.