How to Use These PCB Design Guidelines to Reduce EMI

Introduction

Electromagnetic interference (EMI) is one of the most challenging issues in modern electronic product design. As devices become smaller, faster, and more complex, the potential for EMI problems increases significantly. Proper printed circuit board (PCB) design plays a crucial role in minimizing EMI and ensuring electromagnetic compatibility (EMC). This article presents a comprehensive set of PCB design guidelines that, when properly implemented, can significantly reduce EMI emissions and improve the overall performance of your electronic products.

Understanding EMI in PCB Design

Before diving into specific guidelines, it’s essential to understand the fundamental sources of EMI in PCBs:

- Conducted Emissions: Noise propagated through power and signal traces

- Radiated Emissions: Electromagnetic fields generated by high-frequency signals

- Crosstalk: Unwanted coupling between adjacent traces

- Ground Bounce: Voltage fluctuations in ground connections

EMI problems often manifest as product failures during EMC testing, interference with other devices, or unexpected system behavior. By following these PCB design guidelines, you can address these issues at the design stage, saving time and costs associated with post-production fixes.

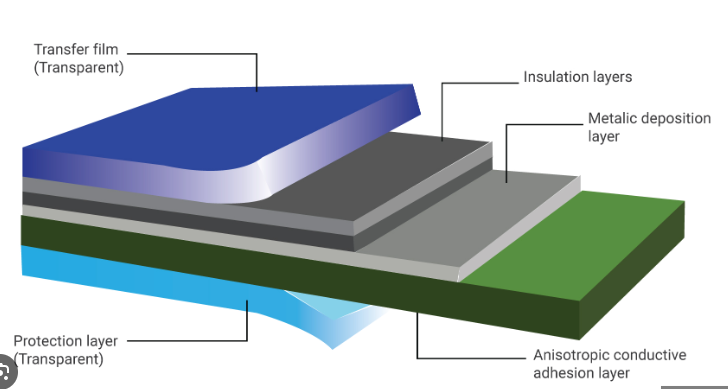

PCB Layer Stackup Guidelines

1. Proper Layer Arrangement

A well-designed layer stackup is the foundation for EMI control:

- Use at least a 4-layer board for complex designs (signal, ground, power, signal)

- For 4-layer boards: Signal1 – Ground – Power – Signal2

- For 6-layer boards: Signal1 – Ground – Signal2 – Power – Ground – Signal3

- Place ground planes adjacent to high-speed signal layers

2. Power Plane Considerations

- Use solid power planes instead of routed power traces when possible

- Keep power and ground planes close together (2-4 mil separation) to enhance decoupling

- Avoid splitting power planes unless absolutely necessary

- If splits are required, minimize the number and route sensitive signals away from splits

Component Placement Strategies

3. Functional Partitioning

- Group components by function (analog, digital, RF, power supplies)

- Separate noisy circuits (switching regulators, clocks) from sensitive ones

- Place high-speed components away from board edges and connectors

4. Clock Circuit Placement

- Position clock generators and oscillators near their load devices

- Keep clock traces as short as possible

- Avoid routing clock signals near board edges or I/O areas

- Use local ground planes under clock circuits

Routing Techniques for EMI Reduction

5. Trace Routing Best Practices

- Keep high-speed traces short and direct

- Avoid sharp angles (use 45° angles or curves)

- Maintain consistent trace widths for impedance control

- Route sensitive signals first, followed by less critical ones

6. Differential Pair Routing

- Maintain consistent spacing between pair members

- Keep pairs symmetrical in length (use meandering if needed)

- Route pairs over continuous reference planes

- Avoid vias in differential pairs when possible

7. Controlled Impedance Routing

- Calculate and maintain proper trace widths for target impedance

- Use appropriate dielectric materials and thicknesses

- Account for impedance changes at vias and layer transitions

- Terminate transmission lines properly to prevent reflections

Grounding Techniques

8. Ground Plane Design

- Use continuous ground planes whenever possible

- Minimize splits and cuts in ground planes

- Provide multiple ground vias for low-impedance return paths

- Implement a ground grid for single-layer boards

9. Mixed-Signal Grounding

- Use a single ground plane for mixed-signal designs (avoid splits)

- Partition analog and digital circuits physically, not through ground splits

- Connect analog and digital grounds at a single point near power entry

10. Grounding for EMI Shielding

- Provide ample ground connections for shields and enclosures

- Use ground stitching vias around board perimeter

- Implement a “ground fence” around noisy circuits

Power Distribution Network (PDN) Design

11. Decoupling Capacitor Placement

- Place decoupling capacitors close to IC power pins

- Use multiple capacitor values in parallel (e.g., 0.1μF, 1μF, 10μF)

- Connect capacitors to ground with low-impedance paths

- Consider using embedded capacitance when appropriate

12. Power Plane Bypassing

- Use multiple vias for power-to-ground connections

- Implement distributed capacitance across the board

- Consider plane capacitance for high-frequency decoupling

Filtering and Shielding Techniques

13. EMI Filter Implementation

- Install filters at power entry points

- Use ferrite beads for high-frequency noise suppression

- Implement π-filters for sensitive power rails

- Place filters close to connectors they protect

14. Board-Level Shielding

- Use ground planes as inherent shields

- Implement guard traces around sensitive signals

- Consider shielded enclosures for critical circuits

- Provide proper grounding for metal shields

Connector and I/O Considerations

15. I/O Filtering

- Filter all I/O lines entering/leaving the board

- Use common-mode chokes on differential I/O

- Implement TVS diodes for ESD protection

- Route filtered signals away from noisy areas

16. Connector Placement

- Group connectors by signal type (power, analog, digital)

- Separate high-speed connectors from sensitive ones

- Provide adequate ground connections for each connector

- Use shielded connectors for high-speed interfaces

Clock and High-Speed Signal Management

17. Clock Distribution

- Use point-to-point routing for critical clocks

- Consider clock buffers instead of long traces

- Implement proper termination for clock lines

- Avoid daisy-chaining clock signals

18. Spread Spectrum Clocking

- Consider SSCG (Spread Spectrum Clock Generation) for clocks > 50MHz

- Evaluate impact on timing margins before implementation

- Verify compatibility with all system components

Design Verification Techniques

19. Pre-Layout Simulation

- Perform signal integrity analysis before routing

- Simulate power distribution network impedance

- Model critical transmission lines

- Analyze potential crosstalk issues

20. Post-Layout Verification

- Conduct Design Rule Checking (DRC) for EMI guidelines

- Perform parasitic extraction and signal integrity analysis

- Verify return current paths

- Check for unintentional antenna structures

Manufacturing Considerations

21. PCB Fabrication Specifications

- Specify controlled impedance requirements

- Define dielectric materials and thicknesses

- Communicate any special EMI-related requirements

- Verify manufacturing tolerances

22. Assembly Process

- Ensure proper component orientation

- Verify decoupling capacitor placement

- Check shield can installation procedures

- Inspect grounding connections

Testing and Troubleshooting

23. EMI Pre-Compliance Testing

- Conduct near-field scans during development

- Identify emission hotspots early

- Compare results with design simulations

- Iterate design based on test findings

24. Common EMI Problems and Solutions

- Excessive clock harmonics: Improve termination or add filtering

- Power plane resonances: Adjust decoupling strategy

- Radiated emissions from cables: Improve I/O filtering

- Ground bounce issues: Enhance ground system

Advanced Techniques for Challenging Designs

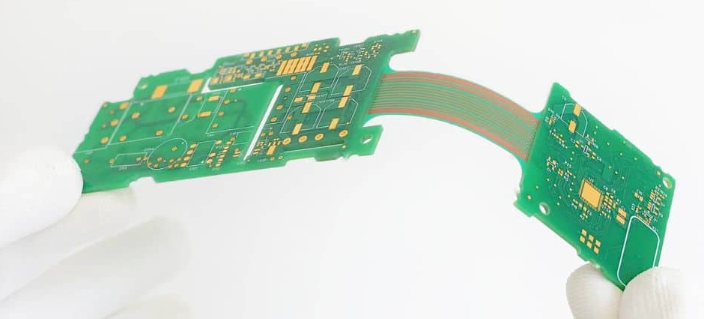

25. High-Density Interconnect (HDI) Considerations

- Manage via stubs in high-speed designs

- Implement back-drilling when necessary

- Consider microvia technology for dense designs

- Pay special attention to return paths in HDI

26. RF and Mixed-Signal Design

- Implement proper RF grounding techniques

- Use coplanar waveguides when appropriate

- Manage analog-digital interference

- Consider cavity structures for sensitive circuits

Conclusion

Implementing these PCB design guidelines systematically can significantly reduce EMI problems in your electronic products. While it may not be practical to apply every recommendation to every design, understanding these principles allows you to make informed trade-offs based on your specific requirements. Remember that EMI control is most effective when considered from the earliest design stages rather than being treated as an afterthought. By incorporating these practices into your design workflow, you’ll improve product reliability, reduce time-to-market, and increase the likelihood of passing EMC compliance testing on the first attempt.

The key to success lies in viewing EMI control as an integral part of the design process rather than a separate concern. Start with good fundamental practices in stackup design and component placement, then refine your approach through careful routing, grounding, and filtering. Combined with proper verification and testing, these guidelines will help you create PCBs that perform well electrically while meeting all necessary EMI requirements.