Analysis of signal integrity in high-speed digital PCB design

With the increase in the output switching speed of integrated circuits and the increase in the density of PCB boards, signal integrity has become one of the issues that must be concerned about in high-speed digital PCB design. Factors such as the parameters of components and PCB boards, the layout of components on PCB boards, and the routing of high-speed signal lines will cause signal integrity problems. For PCB layout, signal integrity requires providing a circuit board layout that does not affect signal timing or voltage, while for circuit routing, signal integrity requires providing termination components, layout strategies, and routing information. High signal speed on PCB, incorrect layout of termination components, or incorrect routing of high-speed signals will cause signal integrity problems, which may cause the system to output incorrect data, the circuit to work abnormally, or even not work at all. How to fully consider the factors of signal integrity in the design process of PCB boards and take effective control measures has become a hot topic in today’s PCB design industry.

1.Signal integrity issues

Good signal integrity means that the signal can respond with the correct timing and voltage level values when needed. Conversely, when the signal cannot respond normally, a signal integrity problem occurs. Signal integrity issues can cause or directly lead to signal distortion, timing errors, incorrect data, address and control lines, system malfunctions, and even system crashes. Signal integrity issues are not caused by a single factor, but by multiple factors in board-level design. IC switching speed, incorrect layout of terminal components, or incorrect wiring of high-speed signals can cause signal integrity issues. The main signal integrity issues include: delay, reflection, synchronous switching noise, oscillation, ground bounce, crosstalk, etc.

2.Definition of signal integrity

Signal integrity refers to the ability of a signal to respond with the correct timing and voltage in a circuit. It is a state in which the signal is not damaged, which indicates the quality of the signal on the signal line.

2.1 Delay

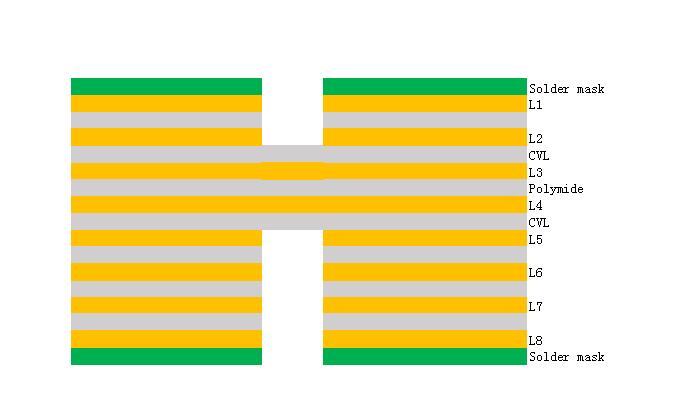

Delay refers to the transmission of a signal at a limited speed on the wire of a PCB board. There is a transmission delay between the signal being sent from the transmitter and the receiver. The delay of the signal will affect the timing of the system. The transmission delay mainly depends on the length of the wire and the dielectric constant of the medium around the wire. In high-speed digital systems, the length of the signal transmission line is the most direct factor affecting the clock pulse phase difference. The clock pulse phase difference refers to the time when two clock signals generated at the same time arrive at the receiving end out of sync. The clock pulse phase difference reduces the predictability of the signal edge arrival. If the clock pulse phase difference is too large, an erroneous signal will be generated at the receiving end. As shown in Figure 1, the transmission line delay has become an important part of the clock pulse cycle.

2.2 Reflection

Reflection is the echo on the sub-transmission line. When the signal delay time (Delay) is much longer than the signal transition time (Transition Time), the signal line must be treated as a transmission line. When the characteristic impedance of the transmission line does not match the load impedance, part of the signal power (voltage or current) is transmitted to the line and reaches the load, but part of it is reflected. If the load impedance is less than the original impedance, the reflection is negative; otherwise, the reflection is positive. Changes in wiring geometry, incorrect line termination, transmission through connectors, and power plane discontinuity can all lead to such reflections.

2.3 Synchronous Switching Noise (SSN)

When many digital signals on a PCB are switched synchronously (such as the data bus and address bus of the CPU), synchronous switching noise will be generated due to the impedance on the power line and the ground line, and ground plane bounce noise (ground bounce) will also appear on the ground line. The strength of SSN and ground bounce also depends on the I/O characteristics of the integrated circuit, the impedance of the power layer and plane layer of the PCB board, and the layout and wiring method of high-speed devices on the PCB board.

2.4 Crosstalk

Crosstalk is the coupling between two signal lines. The mutual inductance and mutual capacitance between the signal lines cause noise on the line. Capacitive coupling causes coupling current, while inductive coupling causes coupling voltage. Crosstalk noise originates from electromagnetic coupling between signal line nets, between signal systems and power distribution systems, and between vias. Crosstalk may cause false clocks, intermittent data errors, etc., affecting the transmission quality of adjacent signals. In fact, we do not need to completely eliminate crosstalk, as long as it is controlled within the range that the system can withstand. PCB board layer parameters, signal line spacing, electrical characteristics of the driver and receiver, and baseline termination methods all have a certain impact on crosstalk.

2.5 Overshoot and Undershoot

Overshoot means that the first peak or valley exceeds the set voltage. For the rising edge, it refers to the highest voltage, and for the falling edge, it refers to the lowest voltage. Undershoot means that the next valley or peak exceeds the set voltage. Excessive overshoot can cause the protection diode to work, resulting in its premature failure. Excessive undershoot can cause false clock or data errors (misoperation).

2.6 Ringing and Rounding

The oscillation phenomenon is the repeated occurrence of overshoot and undershoot. The oscillation of the signal is caused by the transition of inductance and capacitance on the line, which belongs to the underdamped state, while the rounding oscillation belongs to the overdamped state. Oscillation and rounding oscillation are caused by many factors like reflection. Oscillation can be reduced by appropriate termination, but it is impossible to completely eliminate it.

2.7 Ground level bounce noise and reflux noise

When there is a large current surge in the circuit, it will cause ground plane bounce noise. For example, when the outputs of a large number of chips are turned on at the same time, a large transient current will flow through the power plane of the chip and the board. The inductance and resistance of the chip package and the power plane will cause power noise, which will cause voltage fluctuations and changes on the real ground plane (0 V). This noise will affect the operation of other components. The increase in load capacitance, the decrease in load resistance, the increase in ground inductance, and the increase in the number of switching devices will all lead to an increase in ground bounce.

Due to the division of the ground plane (including power and ground), for example, the ground layer is divided into digital ground, analog ground, shielding ground, etc., when the digital signal reaches the analog ground area, ground plane reflux noise will be generated. Similarly, the power layer may also be divided into 2.5 V, 3.3 V, 5 V, etc. Therefore, in multi-voltage PCB design, special attention should be paid to the bounce noise and reflux noise of the ground plane.

3.Signal integrity solution

Signal integrity problems are not caused by a single factor, but by multiple factors in board-level design. The main signal integrity problems include reflection, ringing, ground bounce, crosstalk, etc. The following mainly introduces the solutions to crosstalk and reflection.

3.1 Crosstalk analysis

Crosstalk refers to the unwanted voltage noise interference caused by electromagnetic coupling to adjacent transmission lines when the signal propagates on the transmission line. Excessive crosstalk may cause false triggering of the circuit, resulting in the system not being able to work properly.

Since the size of crosstalk is inversely proportional to the line spacing and proportional to the parallel length of the line. Crosstalk changes with the change of circuit load. For the same topology and wiring conditions, the greater the load, the greater the crosstalk. Crosstalk is proportional to the signal frequency. In digital circuits, the edge change of the signal has the greatest impact on crosstalk. The faster the edge change, the greater the crosstalk. According to the above crosstalk characteristics, the following methods can be summarized to reduce crosstalk:

(1) Reduce the conversion rate of the signal edge when possible.

When selecting devices, slow devices should be selected as much as possible while meeting the design specifications, and different types of signals should be avoided, because fast-changing signals have potential crosstalk risks to slow-changing signals.

(2) The crosstalk generated by capacitive coupling and inductive coupling increases with the increase of the load impedance of the interfered line, so reducing the load can reduce the impact of coupling interference.

(3) When wiring conditions permit, minimize the parallel length between adjacent transmission lines or increase the distance between wires where capacitive coupling may occur, such as using the 3W principle (the distance between the lines must be 3 times the width of a single line or the distance between two lines must be greater than 2 times the width of a single line). A more effective approach is to use ground wires to isolate the wires.

(4) Inserting a ground wire between adjacent signal lines can also effectively reduce capacitive crosstalk. This ground wire needs to be connected to the ground layer every 1/4 wavelength.

(5) Inductive coupling is difficult to suppress.

The number of loops should be reduced as much as possible, the loop area should be reduced, and the signal loops should avoid sharing the same wire.

(6) The signal layers of two adjacent layers should be routed vertically, and parallel routing should be avoided as much as possible to reduce crosstalk between layers.

(7) There is only one reference layer on the surface layer, and the coupling of the surface layer wiring is stronger than that of the middle layer. Therefore, signals that are sensitive to crosstalk should be routed on the inner layer as much as possible.

(8) By terminating, the far end and near end of the transmission line and the terminal impedance are matched with the transmission line, which can greatly reduce crosstalk and reflection interference.

3.2 Reflection analysis

When a signal propagates on a transmission line, as long as it encounters an impedance change, reflection will occur. The main method to solve the reflection problem is to perform terminal impedance matching.

3.2.1 Typical transmission line termination strategy

In high-speed digital systems, impedance mismatch on the transmission line will cause signal reflection. The method to reduce and eliminate reflection is to perform terminal impedance matching at the transmitting end or receiving end according to the characteristic impedance of the transmission line, so that the source reflection coefficient or load reflection coefficient is 0. The termination technology should be used when the length of the transmission line meets the following conditions: L>tr/2tpd. In the formula, L is the length of the transmission line; tr is the rise time of the source signal; and tpd is the load transmission delay per unit length on the transmission line.

There are usually two strategies for terminating a transmission line: matching the load impedance with the transmission line impedance, i.e. parallel termination; matching the source impedance with the transmission line impedance, i.e. serial termination.

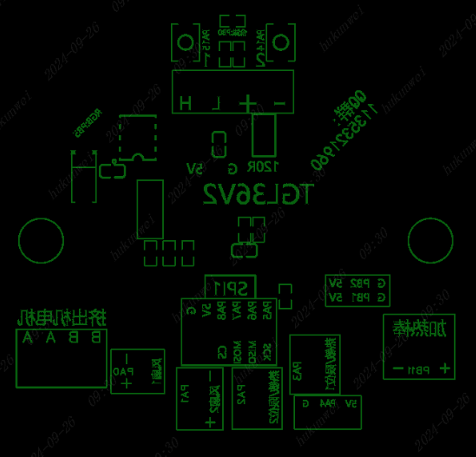

(1) Parallel termination

Parallel termination mainly involves connecting a pull-up or pull-down impedance as close to the load end as possible to achieve impedance matching of the terminal. According to different application environments, parallel termination can be divided into several types as shown in Figure 2.

(2) Serial termination

Serial termination is achieved by inserting a resistor into the transmission line as close to the source end as possible. Serial termination matches the impedance of the signal source. The resistance value of the inserted serial resistor plus the output impedance of the driving source should be greater than or equal to the transmission line impedance. This strategy suppresses the signal reflected from the load (the load end input is high impedance and does not absorb energy) from being reflected from the source end to the load end by making the reflection coefficient at the source end zero.

3.2.2 Termination technology for devices with different processes

The impedance matching and termination technology solutions will also vary with the length of the interconnection and the series of logic devices in the circuit. Only by using the correct and appropriate termination method for specific situations can signal reflection be effectively reduced. Generally speaking, for a CMOS process driver, its output impedance value is relatively stable and close to the impedance value of the transmission line, so using serial termination technology for CMOS devices will achieve better results; while the output impedance of the TTL process driver is different when outputting logic high and low levels, at this time, using the parallel Thevenin termination solution is a better strategy; ECL devices generally have very low output impedance, so using a pull-down termination resistor at the receiving end of the ECL circuit to absorb energy is a common termination technology for the ECL circuit. Of course, the above methods are not absolute. The differences in specific circuits, the selection of network topology, and the number of loads at the receiving end are all factors that can affect the termination strategy. Therefore, when implementing the termination solution of the circuit in a high-speed circuit, it is necessary to select a suitable termination solution according to the specific situation to obtain the best termination effect.

4.Signal integrity analysis modeling

Reasonable circuit modeling simulation is the most common signal integrity solution. In high-speed circuit design, simulation analysis is increasingly showing its superiority. It provides designers with accurate and intuitive design results, making it easy to find problems early and make modifications in time, thereby shortening design time and reducing design costs. There are three commonly used models: SPICE model, IBIS model, and Verilog-A model.

SPICE is a powerful general-purpose analog circuit simulator. It consists of two parts: model equations (Model Equation) and model parameters (Model Parameters). Since the model equation is provided, the SPICE model can be closely connected with the simulator algorithm, which can obtain better analysis efficiency and analysis results; the IBIS model is a model specifically used for digital signal integrity analysis at the PCB board level and system level. It uses I/V and V/T tables to describe the characteristics of digital integrated circuit I/O units and pins. The analysis accuracy of the IBIS model mainly depends on the number of data points and data accuracy of the 1/V and V/T tables. Compared with the SPICE model, the IBIS model has a small amount of calculation.

5.Simulation Verification

Use the asynchronous transceiver example circuit to show the results. In the simulation environment, set the excitation signal to 50 ns, the power supply to 5V, and other settings to default. Simulate the U3-5 pin of the RTSB network. The simulation is shown in Figure 3: Curve a is the signal waveform before termination, and it can be seen that there is serious signal reflection; curves b and c are the signal waveforms after the ground termination resistor, and the termination resistance values are different; curve d is the signal waveform after the Thevenin termination. It can be seen from the figure that the termination resistor can basically eliminate the reflection. The disadvantage is that the termination resistor to the ground causes the ground high level voltage to drop, and the termination resistor to the power supply causes the power supply low level to increase.

6.Conclusion

Based on the continuous development of microelectronics technology, the use of high-speed devices and the design of high-speed digital systems are increasing. The system data rate, clock rate and circuit density are constantly increasing, and the design requirements for PCB boards are also getting higher and higher, especially the signal integrity problem. To ensure that the PCB has good signal integrity, it is necessary to integrate multiple influencing factors, reasonably layout and wiring, so as to improve product performance.