Analysis of Solutions for PCB Impedance Discontinuity

Abstract

Impedance discontinuity in printed circuit boards (PCBs) is a critical issue affecting signal integrity in high-speed digital and RF circuits. This paper examines the root causes of impedance discontinuities, analyzes their impact on signal quality, and presents comprehensive solutions including design optimization techniques, material selection strategies, and manufacturing controls. The analysis covers both common approaches and advanced mitigation methods to maintain consistent impedance throughout PCB transmission lines.

Keywords: PCB design, impedance control, signal integrity, transmission line, high-speed design

1. Introduction

As electronic systems continue to operate at higher frequencies and faster edge rates, maintaining controlled impedance throughout PCB interconnects has become essential. Impedance discontinuities occur when there are variations in the characteristic impedance along a transmission path, leading to signal reflections, distortion, and potential system failures. Industry reports indicate that impedance-related issues account for approximately 30% of signal integrity problems in high-speed designs (IPC, 2022).

This paper systematically examines solutions for minimizing impedance discontinuities across four key areas: PCB stackup design, trace routing techniques, material considerations, and manufacturing controls. The analysis incorporates both theoretical foundations and practical implementation guidelines.

2. Fundamentals of Impedance Discontinuity

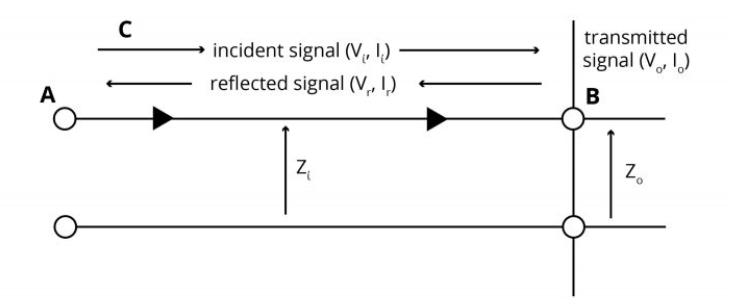

2.1 Characteristic Impedance Basics

The characteristic impedance (Z₀) of a PCB transmission line is determined by:

Z₀ = √(L/C)

Where L is the distributed inductance and C is the distributed capacitance per unit length. For microstrip lines, the impedance can be approximated by:

Z₀ = [87/√(ε_r + 1.41)] × ln[5.98h/(0.8w + t)]

Where ε_r is the dielectric constant, h is the dielectric height, w is the trace width, and t is the trace thickness.

2.2 Common Sources of Discontinuity

Major causes of impedance variations include:

- Layer transitions (vias)

- Changes in trace geometry (width, thickness)

- Dielectric material variations

- Reference plane gaps

- Connector interfaces

- Bends and corners in routing

- Solder mask coverage differences

3. Design-Level Solutions

3.1 Stackup Optimization

Proper PCB stackup design forms the foundation for impedance control:

- Symmetrical Construction: Balanced dielectric thicknesses above and below signal layers minimize warpage and impedance variation

- Controlled Dielectric Thickness: Maintain consistent dielectric spacing (±10% tolerance)

- Reference Plane Management: Ensure uninterrupted reference planes beneath critical traces

Table 1: Recommended Stackup Configurations for Common Impedance Values

| Target Z₀ (Ω) | Trace Width (mil) | Dielectric Thickness (mil) | ε_r |

|---|---|---|---|

| 50 | 8.5 | 5.2 | 4.0 |

| 75 | 5.2 | 7.8 | 3.6 |

| 90 | 3.8 | 5.1 | 3.2 |

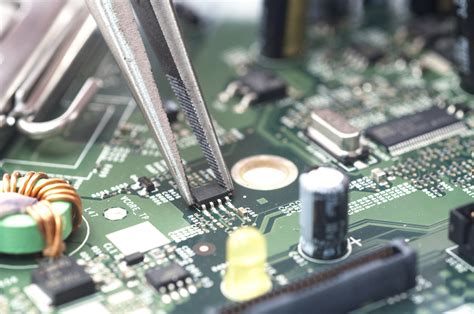

3.2 Trace Routing Techniques

3.2.1 Microstrip to Stripline Transitions

When signals transition between layers:

- Use matched via structures with appropriate anti-pads

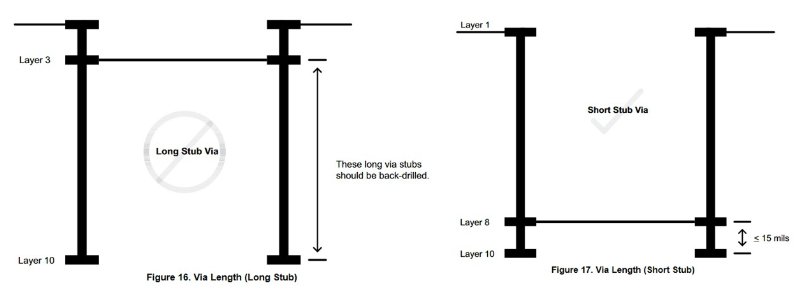

- Implement back-drilling for thick boards (>100 mil)

- Apply stitching capacitors near transitions (0.1-1nF)

3.2.2 Bend Compensation

For 90° turns:

- Mitre bends (45° chamfer) reduce discontinuity by 60% compared to square corners

- Optimal mitre = 1.414 × trace width

3.2.3 Width Transition Management

For necessary trace width changes:

- Implement tapered transitions (length > 3× width difference)

- Follow the rule: ΔZ < 5% per transition point

3.3 Differential Pair Considerations

Maintain:

- Constant spacing (±10%) between pair members

- Balanced length matching (<5 mil difference)

- Avoid antipodal routing over plane splits

4. Material Selection Solutions

4.1 Dielectric Material Properties

Key parameters affecting impedance consistency:

- Dielectric Constant (Dk): Variation < 2% across panel

- Loss Tangent: Lower values (≤0.02) reduce frequency-dependent effects

- Thickness Tolerance: ≤±5% for critical layers

4.2 Copper Foil Considerations

- Use low-profile copper (≤12μm roughness) for high-frequency signals

- Specify reverse-treated foil for consistent etch characteristics

- Maintain 1 oz/ft² (35μm) base weight for controlled thickness

4.3 Solder Mask Impact

- Open window design over critical traces reduces capacitance variation

- If coverage needed, use thin (≤15μm) liquid photoimageable (LPI) masks

- Account for ≈2Ω impedance reduction with mask coverage

5. Manufacturing Control Solutions

5.1 Fabrication Tolerances

Critical manufacturing parameters to specify:

- Etch compensation: ±0.2 mil accuracy

- Dielectric thickness: ±3% tolerance for impedance-critical layers

- Impedance testing: 100% verification on coupons

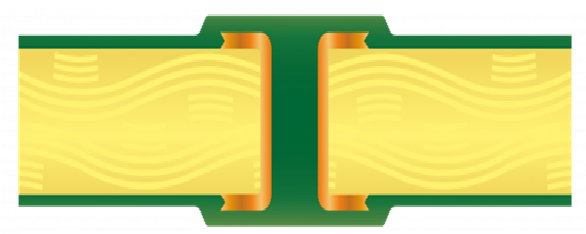

5.2 Via Optimization Techniques

- Via-in-Pad with filled and capped vias for BGA breakouts

- Microvias (<6 mil diameter) for HDI designs

- Via Stub Elimination through back-drilling or layer-specific drilling

5.3 Surface Finish Considerations

Finish options in order of impedance stability:

- Electroless Nickel Immersion Gold (ENIG): ±1Ω variation

- Immersion Silver: ±1.5Ω variation

- Organic Solderability Preservative (OSP): ±2Ω variation

- HASL: Not recommended for impedance-critical designs

6. Advanced Mitigation Techniques

6.1 Embedded Passive Components

- Integrate termination resistors within PCB layers

- Laser-trimmed thin-film resistors for precise values (±1%)

6.2 3D Field Solvers

Modern simulation tools:

- HFSS, CST, and SIwave provide accurate discontinuity analysis

- Enable “what-if” scenarios for complex transitions

- Can predict impedance variations within 2% of measured values

6.3 Active Compensation Circuits

For unavoidable discontinuities:

- Programmable pre-emphasis drivers

- Continuous-time linear equalization (CTLE)

- Decision feedback equalization (DFE) receivers

7. Verification Methods

7.1 Time Domain Reflectometry (TDR)

- Resolution: ≤10ps rise time

- Accuracy: ±1Ω for modern instruments

- Test structure requirements: ≥3″ line length

7.2 Vector Network Analysis (VNA)

- Frequency range: DC to 20+ GHz

- S-parameter analysis (S11, S21)

- Permits material characterization

7.3 Cross-Section Analysis

- Verifies actual dielectric thicknesses

- Measures copper profile and etch quality

- Validates via plating uniformity

8. Case Study Examples

8.1 DDR4 Memory Interface

Problem: 5Ω impedance spikes at DIMM socket transitions

Solution:

- Implemented via-in-pad with 0.25mm diameter laser vias

- Added ground stitching vias within 100mil of transitions

Result: Reduced reflection noise by 40%

8.2 28Gbps SerDes Channel

Problem: 12% eye closure due to package-to-board discontinuity

Solution:

- Designed stepped impedance transition (40Ω-50Ω-40Ω)

- Used 3D EM simulation to optimize transition length

Result: Achieved 92% eye opening compliance

9. Conclusion

Effective management of PCB impedance discontinuities requires a holistic approach spanning design, materials, and manufacturing. Key findings from this analysis include:

- Stackup symmetry and consistent dielectric properties provide the foundation for impedance control

- Geometric transitions require careful analysis and compensation, particularly for high-speed signals

- Advanced simulation tools enable precise discontinuity prediction before fabrication

- Manufacturing controls must be implemented to maintain design intent

- Verification testing is essential to validate impedance performance

As data rates continue increasing toward 112Gbps and beyond, impedance control will remain a critical factor in PCB design success. Future developments in low-Dk materials, additive manufacturing processes, and integrated passives promise to provide additional solutions for impedance discontinuity challenges.