Artificial intelligence “invades” chip manufacturing

Artificial intelligence (AI) is currently transforming multiple industries. There is an interesting phenomenon: artificial intelligence is helping to promote the advancement of artificial intelligence chips. As early as June 2021, Google used AI to design its TPU chip. Google said that artificial intelligence can complete chip design work that takes months to complete manually in less than 6 hours. A commentary in Nature called the research an “important achievement” and pointed out that such work can help offset the end of Moore’s Law. In addition, Nvidia has begun to use artificial intelligence to effectively improve and accelerate GPU design; Samsung has also talked about using artificial intelligence to design chips.

But this is far from the only application of artificial intelligence-assisted chips. AI technology is penetrating into more core links of the chip industry, and AI is also quietly exerting its strength in the key links of manufacturing this chip industry chain.

In the chip manufacturing link, the yield is increasingly tested

Now almost all applications, including 5G, the Internet of Things, automobiles, data centers, etc., are based on chips with higher performance, lower power consumption, and greater computing power. The demand for chips has increased significantly, but the supply of chips cannot keep up with the demand. Improving the yield of existing products is an effective measure recognized by the industry.

However, the improvement of yield has brought great challenges to both chip designers and manufacturers.

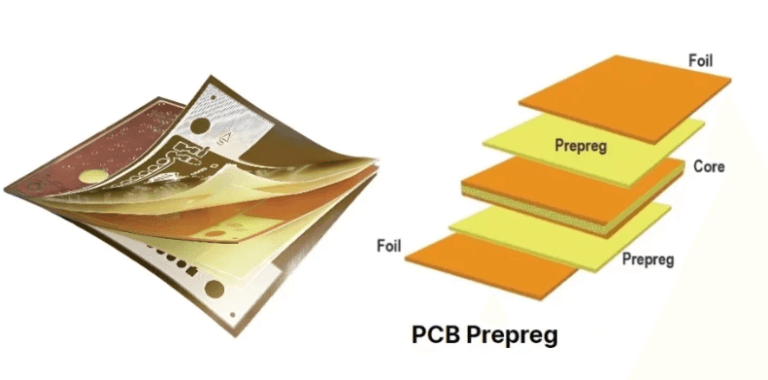

Manufacturing is a key link in the semiconductor industry chain. The entire manufacturing process is mainly divided into eight steps: wafer processing – oxidation – lithography – etching – thin film deposition – interconnection – testing – packaging, and each chip manufacturing step requires hundreds of processes. The chip production cycle is often two or three months. The amount of data generated during the production process is huge, and the parameter variables involved are numerous. Any slight change can affect the final chip yield.

The process evolution following Moore’s Law is one of the most effective ways for chips to achieve high-performance computing, and it is also the direction pursued by the industry. As the chip process reaches more advanced 5nm and 3nm, the complexity of chip design increases exponentially, the production process continues to lengthen, and the manufacturing of chips becomes extremely complex and precise, and the yield becomes extremely challenging. According to Applied Materials, a giant semiconductor equipment supplier, the number of process steps in chip manufacturing has increased by 48% from 2015 to 2021. Compared with mature nodes, the baseline yield of advanced nodes is also getting lower and lower.

In the commercialization process of semiconductors, yield is directly related to chip output, production costs and corporate profitability.

Therefore, it is becoming increasingly difficult to improve PPA only through improvements in chip process technology, and from a cost-effectiveness perspective, the cost of chip tapeout is becoming increasingly expensive, and only a very small number of chip companies can afford it.

Therefore, in order to improve chip yield and be economically feasible, we must take a multi-pronged approach and explore innovative methods. In today’s highly automated era, the introduction of technologies such as artificial intelligence/machine learning can promote chip manufacturing processes and improve chip yields, thereby helping us quickly bridge the gap between computing power supply and demand.

AI’s strong attack

Chip manufacturing is one of the most expensive production processes in the world. Chip output determines the success or failure of wafer manufacturers such as Intel, Samsung, and TSMC. They invest a lot of resources to keep wafer fabs operating around the clock to maximize long-term profits.

Semiconductor manufacturers need to rely on scanning, testing, and diagnosis to help fault analysis to solve yield problems.

Back-end defect detection is undoubtedly a major “gatekeeper” for improving chip yield. Most advanced SoCs now use extremely small manufacturing processes, and some even introduce EUV lithography technology, which makes it more difficult for manufacturers to locate tiny faults and defects on chips; and when manufacturing 3D structures and performing complex multi-patterning steps, some of these small differences will accumulate to produce yield-inhibiting defects. If some of these tiny differences are detected late, then all subsequent process steps are basically a waste of time and money. The longer they find defects, the more money they lose.

To solve this industry problem, semiconductor equipment supplier Applied Materials has incorporated artificial intelligence into the wafer inspection process.

Since 2016, Applied Materials has used ExtractAI technology to develop the Enlight system, and in 2020 launched a new generation of Enlight optical semiconductor wafer inspection machines, which introduced big data and AI technology. The Enlight system can map millions of potential defects on a wafer in less than an hour.

Applied Materials said that by combining their Enlight optical inspection, ExtractAI technology and SEMVision eBeam review capabilities, they have solved the most difficult inspection challenges: distinguishing defects that affect yield from noise, and learning and adapting to process changes in real time. And by generating big data, the Enlight system reduces the cost of capturing critical defects by 3 times. This will allow fabs to receive more actionable data faster than ever before, thereby reducing cost of ownership and accelerating production and time to market. Currently, these latest tool sets have been installed in multiple fabs, which are using it to shorten the yield of the latest technology.

Applied Materials said that Enlight is the first system in its product line to use artificial intelligence to improve the production process, and more artificial intelligence-enhanced systems are in preparation.

Inspection equipment is a measure to improve yield in the post-manufacturing stage.

If the necessary measures can be taken in the physical design stage of IC development, the control of yield can be gradually transferred to the front-end design of the chip to ensure that the design can be accurately manufactured, then the yield can be increased and defects that may occur after the product is delivered to the customer can be prevented. This is called DFM (Design-for-Manufacture) in the industry, and the concept exists in almost all engineering disciplines.

In DFM on the chip design side, EDA vendors are working to integrate various AI functions into the tool flow.

For example, Siemens EDA’s Calibre SONR tool has a built-in machine learning engine TensorFlow. By integrating parallel computing and ML technology into EDA tools, EDA tools can run faster. The Calibre physical verification platform covers the layout and mask of signoff-level verification and all verification steps in the chip manufacturing process. Calibre’s product line is still expanding, and through the complementary advantages between products, it can truly extend from the chip design end to the chip manufacturing end. This can not only help designers to implement physical verification and delivery design with confidence, but also greatly improve the tape-out yield, shorten the time to market of chip products and accelerate the speed of innovation.

Simulation has always been a pain for chip designers. With the development of advanced processes and ultra-low voltage, the simulation field faces pain points such as large data volume, long timing library extraction time, too slow brute force exhaustive, and insufficient accuracy of STA tools for internal difference method. If machine learning algorithms are used to analyze existing databases in a big data way, multiple surface models are interconnected to build a multidimensional model, and a new database under the corner is inferred through the creation of such a model. Compared with SPICE simulation or internal difference method, this method can be said to be cross-generation competition, with huge advantages in both speed and accuracy. The Solido machine learning technology launched by Siemens EDA can accelerate the extraction of a single timing library file by nearly 100 times (compared with the traditional SPICE method), and increase the extraction speed of the entire timing library by 2 to 3 times, while also keeping the accuracy within an acceptable range.

Verification is also becoming increasingly complex and difficult with the complexity of SoC, and the proportion of verification work in chip research and development is also increasing, because such heavy verification work must be guaranteed to be 100% correct to ensure the success of tape-out. Regarding this challenge, AI can also be handed over. Machine learning is used to automatically select parser strategies to execute assertion proofs related to formal verification in Siemens EDA OneSpin.

As processes and designs move forward, the root causes of yield loss become more and more complex, fault isolation technology faces challenges, and improving diagnostic resolution becomes the top priority to reduce yield ramp-up time. In this regard, Siemens EDA’s Tessent Diagnosis’s layout perception and cell perception technology, combined with Tessent YieldInsight’s unsupervised machine learning technology, Root Cause Deconvolution (RCD for short), can find the most likely defect distribution and remove low-probability suspects, thereby improving resolution and accuracy. Currently, GlobalFoundries, UMC, and SMIC are using this technology to quickly locate the exact root cause that affects the yield and quickly achieve yield improvement.

It can be seen that with the help of AI/ML technology, EDA tools are increasingly becoming a powerful tool for solving yield climbing. Artificial intelligence/machine learning can already play a powerful role in new areas of automated IC design, such as yield climbing at advanced process nodes, machine learning technology in standard cell variable-aware timing library feature extraction, application in mass production diagnosis-driven yield analysis, and significantly shortening ASIC/FPGA verification cycles.

Conclusion

Through the innovation of chip manufacturers in various fields, artificial intelligence technology has shown its advantages in many fields. The application of AI can not only significantly shorten the time required for chip design, the time for chip defect detection, and reduce the labor costs of chip design companies, but also effectively meet the market’s demand for the complexity of integrated circuits. Using artificial intelligence technology to help design and manufacture chips has become a general trend. I believe that in the near future, there will be more exploration and application of artificial intelligence technology in the field of chip production.