How to Reduce Signal Attenuation in High-Speed PCBs

Introduction

Signal attenuation is one of the most critical challenges in high-speed printed circuit board (PCB) design. As digital systems continue to push towards higher frequencies and faster edge rates, maintaining signal integrity becomes increasingly difficult. Signal attenuation can lead to distorted waveforms, timing errors, and ultimately system failures. This article explores comprehensive strategies to minimize signal attenuation in high-speed PCBs, covering material selection, design techniques, and manufacturing considerations.

Understanding Signal Attenuation in High-Speed PCBs

Signal attenuation in high-speed PCBs primarily occurs through two mechanisms:

- Conductor Losses: Resistance in the copper traces causes energy to be dissipated as heat. At high frequencies, skin effect exacerbates these losses by forcing current to flow only in a thin layer near the conductor’s surface.

- Dielectric Losses: The PCB substrate material absorbs some of the signal’s energy due to its imperfect insulating properties. This loss is quantified by the dissipation factor (Df) or loss tangent.

The total attenuation (α) can be expressed as:

α = α_conductor + α_dielectric

Where both components increase with frequency, making attenuation particularly problematic for multi-gigabit designs.

Material Selection Strategies

1. Low-Loss Dielectric Materials

The choice of PCB substrate material significantly impacts dielectric losses:

- Standard FR-4: Typically has a dissipation factor around 0.02 at 1 GHz, which may be unacceptable for signals above 5 Gbps

- High-Performance Alternatives:

- Rogers RO4000 series (Df ≈ 0.004)

- Isola I-Tera (Df ≈ 0.005)

- Nelco N4000-13 (Df ≈ 0.008)

- Megtron 6 (Df ≈ 0.002)

When selecting materials, consider:

- Dielectric constant (Dk) consistency across frequency

- Thermal stability

- Moisture absorption

- Cost and manufacturability

2. Copper Foil Selection

The copper surface roughness significantly affects conductor losses:

- Standard ED (Electrodeposited) Copper: Rough surface increases effective resistance at high frequencies

- Low-Profile Alternatives:

- RTF (Reverse Treat Foil)

- HVLP (Hyper Very Low Profile)

- Rolled annealed copper

Smoother copper can reduce conductor losses by 15-30% at 10 GHz compared to standard ED copper.

Design Techniques to Minimize Attenuation

1. Optimal Trace Geometry

- Width Considerations:

- Wider traces reduce DC resistance but increase capacitive coupling

- Balance between characteristic impedance and loss

- Typical high-speed traces range from 4-8 mils for 50Ω microstrips

- Thickness Selection:

- Thicker copper reduces resistance but may require wider traces to maintain impedance

- Consider 1 oz (35 μm) or 0.5 oz (17.5 μm) copper based on current requirements

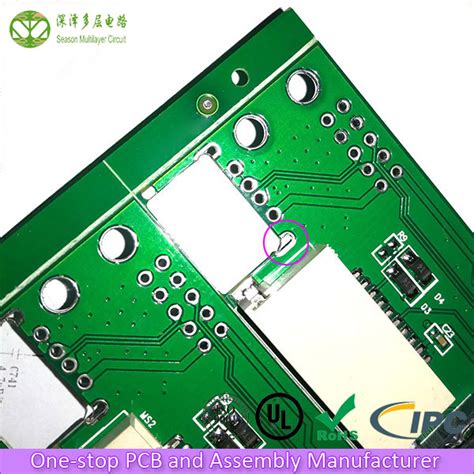

2. Proper Stackup Design

A well-designed stackup can significantly reduce losses:

- Use symmetrical construction to prevent warpage

- Place critical high-speed layers adjacent to low-loss prepreg

- Minimize the distance to reference planes to reduce fringing fields

- Consider using hybrid stackups with high-performance materials only where needed

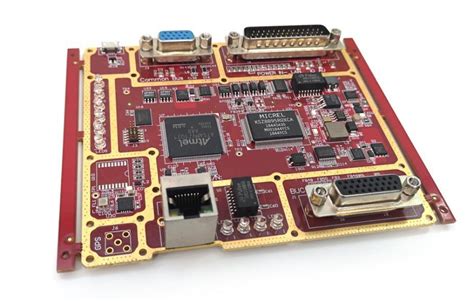

3. Via Optimization

Vias are major sources of signal degradation:

- Use back-drilling to remove unused via stubs

- Implement via-in-pad with filled vias for dense BGA breakouts

- Maintain consistent return paths through stitching vias

- Consider via diameter and pad size to minimize impedance discontinuities

4. Termination Strategies

Proper termination prevents reflections that can exacerbate losses:

- Use source termination for point-to-point links

- Implement parallel termination for multi-drop buses

- Consider active termination for very high-speed interfaces

- Match termination values precisely to trace impedance

Manufacturing Considerations

1. Impedance Control

Maintaining consistent impedance reduces reflections and effective loss:

- Specify impedance tolerance (typically ±10%)

- Require impedance testing coupons on production panels

- Account for manufacturing variations in dielectric thickness

2. Surface Finish Selection

The PCB finish affects signal loss and reliability:

- ENIG (Electroless Nickel Immersion Gold): Common but nickel introduces some loss

- Immersion Silver: Lower loss but susceptible to tarnishing

- OSP (Organic Solderability Preservative): Lowest loss but limited shelf life

- Electrolytic Hard Gold: Durable but highest loss

3. Plating Quality

Ensure consistent copper plating in vias and through-holes:

- Specify plating thickness (typically 1 mil minimum)

- Require cross-sectioning for quality verification

- Monitor for voids or uneven deposition

Advanced Techniques for Extreme High-Speed Designs

1. Equalization

Implement signal conditioning to compensate for losses:

- Transmitter Pre-emphasis: Boosts high-frequency components

- Receiver Equalization: Recovers attenuated signals

- CTLE (Continuous Time Linear Equalization)

- DFE (Decision Feedback Equalization)

2. Alternative Transmission Media

For extremely high-speed applications (>56 Gbps):

- Coaxial PCB Embedding: Integrate coaxial structures within PCB

- Optical Interconnects: Use polymer waveguides for optical signaling

- Terahertz Transmission: Emerging technologies for beyond 100 Gbps

3. 3D Electromagnetic Simulation

Use advanced simulation tools to predict and optimize performance:

- Full-wave 3D solvers for critical structures

- Loss analysis across frequency bands

- Sensitivity analysis for manufacturing variations

Measurement and Validation

1. Time Domain Reflectometry (TDR)

- Characterize impedance variations along transmission lines

- Identify discontinuities causing reflections

- Measure actual propagation velocity

2. Vector Network Analyzer (VNA) Measurements

- Measure S-parameters (S21 for insertion loss)

- Characterize loss versus frequency

- Validate dielectric and conductor loss models

3. Eye Diagram Analysis

- Assess system-level performance

- Evaluate margin against specifications

- Validate equalization effectiveness

Future Trends in Low-Loss PCB Technology

- Ultra-Low Loss Materials: Development of new dielectric materials with Df < 0.001

- Advanced Copper Treatments: Atomic-level surface smoothing techniques

- Air-Dielectric Structures: Using air gaps to minimize dielectric loss

- Photonic Integration: Combining optical and electrical signaling

- Machine Learning Optimization: AI-driven design of low-loss interconnects

Conclusion

Reducing signal attenuation in high-speed PCBs requires a holistic approach encompassing material science, careful design practices, and precision manufacturing. By understanding the fundamental loss mechanisms and implementing the strategies outlined in this article, designers can successfully develop PCBs that maintain signal integrity at multi-gigabit data rates. As speeds continue to increase, staying abreast of emerging materials and technologies will be essential for pushing the boundaries of high-speed digital design.

The key takeaways for minimizing signal attenuation are:

- Select appropriate low-loss materials for both dielectric and conductors

- Optimize trace geometry and stackup design

- Implement proper termination and via design

- Work closely with manufacturers to control impedance and plating quality

- Utilize advanced techniques like equalization when necessary

- Thoroughly validate designs through measurement and simulation

By systematically addressing each of these areas, engineers can significantly reduce signal attenuation and ensure robust performance in even the most demanding high-speed applications.