Reflection Analysis and Simulation in High-Speed PCB Designs

Abstract

With the increasing demand for high-speed digital circuits, signal integrity (SI) has become a critical factor in printed circuit board (PCB) design. One of the major challenges in high-speed designs is signal reflection, which can lead to data corruption, timing errors, and reduced system performance. This paper explores the causes of signal reflections in high-speed PCBs, analyzes their impact on signal integrity, and discusses simulation techniques to mitigate these effects. Using electromagnetic (EM) simulation tools such as Ansys HFSS, Cadence Sigrity, and Keysight ADS, we demonstrate how to model transmission lines, identify reflection sources, and optimize PCB layouts to minimize signal degradation.

1. Introduction

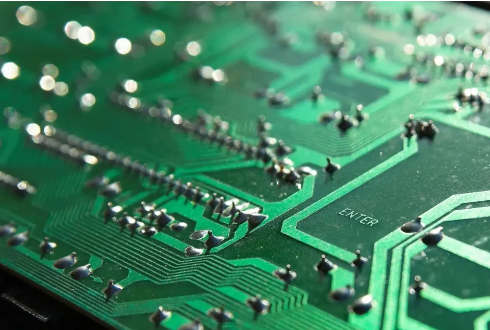

High-speed PCB designs operate at frequencies where signal wavelengths are comparable to the physical dimensions of the traces. At these frequencies, transmission line effects dominate, and impedance mismatches can cause signal reflections. These reflections result in overshoot, undershoot, and ringing, degrading signal quality and potentially causing logic errors.

This paper examines:

- The physics behind signal reflections in transmission lines.

- Key factors contributing to impedance mismatches.

- Simulation methodologies to analyze and mitigate reflections.

- Practical design guidelines for minimizing reflections in high-speed PCBs.

2. Fundamentals of Signal Reflections

2.1 Transmission Line Theory

In high-speed PCBs, traces behave as transmission lines when the signal rise time is shorter than the propagation delay across the trace. The characteristic impedance ((Z_0)) of a transmission line is given by:

[

Z_0 = \sqrt{\frac{L}{C}}

]

where (L) is the inductance per unit length and (C) is the capacitance per unit length.

When a signal encounters an impedance discontinuity (e.g., a via, connector, or change in trace width), part of the signal reflects back toward the source. The reflection coefficient ((\Gamma)) is defined as:

[

\Gamma = \frac{Z_L – Z_0}{Z_L + Z_0}

]

where (Z_L) is the load impedance.

2.2 Causes of Reflections

Common sources of reflections in high-speed PCBs include:

- Impedance Mismatches: Variations in trace width, dielectric thickness, or reference plane changes alter (Z_0).

- Stubs and Vias: Unused trace segments (stubs) introduce parasitic capacitance, while vias add impedance discontinuities.

- Termination Errors: Improper termination (e.g., missing or mismatched resistors) leads to reflections.

- Connectors and IC Packages: Transition points between PCBs and components often introduce impedance variations.

3. Impact of Reflections on Signal Integrity

Reflections cause several signal integrity issues:

- Overshoot/Undershoot: Excessive voltage spikes due to reflected waves.

- Ringing: Damped oscillations that prolong settling time.

- Timing Jitter: Signal distortions that affect clock synchronization.

- Eye Diagram Closure: Reduced margin in high-speed serial links (e.g., PCIe, DDR).

4. Simulation Techniques for Reflection Analysis

4.1 Time-Domain Reflectometry (TDR)

TDR simulations inject a step signal into a transmission line and measure reflected waves to identify impedance variations. Tools like Keysight ADS provide TDR analysis to locate discontinuities.

4.2 Frequency-Domain S-Parameter Analysis

Scattering parameters (S-parameters) characterize reflection ((S_{11})) and transmission ((S_{21})) behavior. High (S_{11}) indicates strong reflections.

4.3 3D Electromagnetic (EM) Simulation

Full-wave EM solvers (e.g., Ansys HFSS) model complex structures like vias and connectors, providing accurate reflection analysis.

4.4 Example: Simulating a Microstrip Line

Using Cadence Sigrity, we simulate a 50Ω microstrip line with a 75Ω discontinuity:

- Model Setup: Define trace geometry, dielectric properties, and port terminations.

- TDR Response: Observe impedance variations and reflection peaks.

- Optimization: Adjust trace width or add termination to minimize (\Gamma).

5. Mitigation Strategies

5.1 Impedance Matching Techniques

- Series Termination: Adds a resistor near the driver to match source impedance.

- Parallel Termination: Places a resistor at the load to absorb reflections.

- AC Termination: Uses an RC network for high-speed signals.

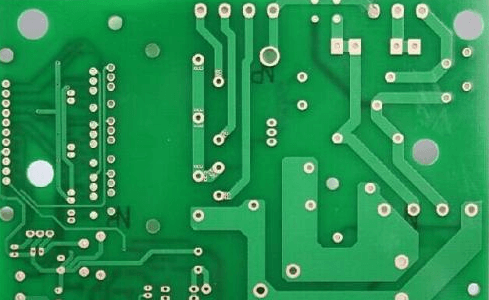

5.2 PCB Layout Best Practices

- Maintain consistent trace width and spacing.

- Minimize stub lengths and avoid sharp bends.

- Use ground planes to ensure a continuous return path.

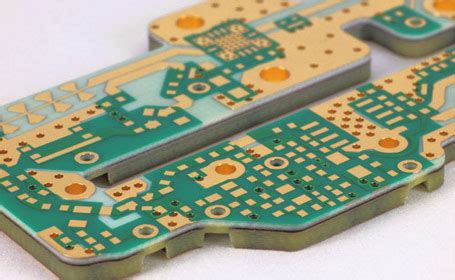

5.3 Via Optimization

- Use back-drilled or blind vias to reduce stub effects.

- Implement via shielding in high-frequency designs.

6. Case Study: DDR4 Memory Interface

A DDR4 bus operating at 3200 Mbps was experiencing timing errors due to reflections from improperly routed traces. Using HyperLynx simulations, we identified impedance mismatches at via transitions and optimized the layout with:

- Controlled impedance routing.

- Proper termination resistors.

- Reduced via stub lengths.

Post-optimization, the eye diagram showed improved signal quality, confirming reflection reduction.

7. Conclusion

Signal reflections in high-speed PCBs degrade performance and must be carefully analyzed through simulation. By applying transmission line theory, EM modeling, and proper termination techniques, designers can minimize reflections and ensure robust signal integrity. Future work includes machine learning-based optimization for ultra-high-speed designs beyond 100 GHz.