When designing a multi-rail power supply, device placement and routing are important!

In power supply design, careful placement and routing are critical to achieving a good design, leaving enough room for size, accuracy, efficiency, and avoiding problems in production. We can leverage years of test experience and the expertise of layout engineers to finally get the board produced.

Efficiency of Careful Design

The design may look fine on paper (that is, from a schematic perspective) and even during simulation, but the real test is after layout, PCB manufacturing, and prototype stress testing by loading the circuit. This section uses real-world design examples to introduce some tips to help avoid pitfalls. We will introduce several important concepts to help avoid design flaws and other pitfalls that may require a future redesign and/or re-spin of the PCB.

Power Budget

You need to be aware of systems that operate as expected in normal conditions, but do not operate as expected when in full speed mode or when unstable data starts to appear (after noise and interference have been eliminated).

When exiting the cascade stage, avoid current limiting conditions. A typical cascade application: (A) shows a design consisting of an ADP5304 buck regulator (PSU1) that generates a 3.3 V supply with a maximum current of 500 mA. To improve efficiency, designers should tap off the 3.3 V rail instead of the 5 V input supply. The 3.3 V output is further cut off to power PSU2 (LT1965), an LDO regulator that is used to further step down the voltage to 2.5 V and limit the maximum output current to 1.1 A as required by the onboard 2.5 V circuits and ICs.

There are some typical hidden problems with this system.

It works fine under normal circumstances. However, when the system initializes and starts running at full speed – for example, when the microprocessor and/or ADC starts sampling at high speed – problems arise. Since no regulator can generate a higher voltage at the output than at the input, the maximum power (P = V × I) at VOUT1 used to power the combined circuits VOUT1 and VOUT2 is 3.3 V × 0.5 A = 1.65 W. This number assumes 100% efficiency, but the actual power is less because of losses in the power delivery process. Assume that the maximum available power from the 2.5 V rail is 2.75 W. If the circuit tries to draw this much power and this requirement is not met, it will behave erratically when PSU1 starts to limit current. The current may start to limit due to PSU1, or worse, some controllers shut down completely due to overcurrent.

If implemented after successful troubleshooting, a higher power controller may be required.

The best case is to replace it with a pin-compatible, higher current device; the worst case is to completely redesign and remanufacture the PCB. If you consider the power budget before the conceptual design phase begins, you can avoid potential project schedule delays.

With this in mind, create a realistic power budget before selecting a controller. Include all the power rails you need: 2.5 V, 3.3 V, 5 V, etc. Include all the pull-up resistors, discrete devices, and ICs that will consume power for each rail. Use these values to work backwards to estimate the power supplies you will need. Use a power tree system design tool such as LTpowerPlanner to easily create a power tree that supports the required power budget.

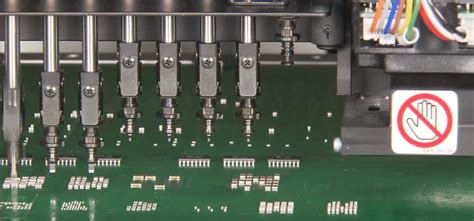

Layout and Routing

Proper layout and routing can avoid current limitations caused by burned tracks due to wrong trace widths, wrong vias, insufficient number of pins (connectors), wrong contact size, etc. The following sections describe some of the areas to watch out for and also provide a few PCB design tips.

Connectors and Pin Headers

Extending the total current of the example to 17 A, the designer must consider the current handling contact capabilities of the pins. Generally speaking, the current carrying capacity of a pin or contact is affected by several factors such as the size of the pin (contact area), metal composition, etc. A typical 1.1 mm diameter male through-hole connector pin carries about 3 A. If 17 A is needed, make sure your design has enough pins to handle the total current carrying capacity. This can be easily accomplished by increasing the current carrying capacity of each conductor (or contact) and leaving some safety margin so that it carries more than the total current consumption of the PCB circuit. In this example, 6 pins are needed to achieve 17 A (with 1A headroom). A total of 12 pins are needed for V CC and GND. To reduce the number of contacts, consider using power jacks or larger contacts.

Routing

Use available online PCB tools to help determine the current capacity of your layout. A one-ounce copper PCB with a 1.27 mm track width will carry about 3 A, and a 3 mm track width will carry about 5 A. Leave some headroom, so a 20 A track width would need to be 19 mm (about 20 mm) (note that this example does not account for the effects of temperature rise). Because of the space constraints of the PSU and system circuitry, a 20 mm track width is not possible. To solve this problem, a simple solution is to use a multi-layer PCB. Reduce the track width to (for example) 3 mm and replicate these tracks on all layers in the PCB to ensure that the sum of the tracks (in all layers) can achieve a current carrying capacity of at least 20 A.

Vias and Connections

In the via example, the via is connecting multiple power layers of the controller’s PCB. If you choose a 1 A via, but need 2 A of current, the track width must be able to carry 2 A of current and the via connection must also be able to handle this current. The example requires at least two vias (preferably three if space allows) to connect the current to the power layer. This problem is often overlooked and only one via is used to make the connection. After the connection is made, the via acts as a fuse, which blows and disconnects the power connection to the adjacent layer. Poorly designed vias are difficult to improve and solve later because the blown via is difficult to notice or is covered by other components.

Note the following parameters regarding vias and PCB tracks: Track width, via size, and electrical parameters are affected by several factors, such as PCB finish, routing layers, operating temperature, etc., which ultimately affect current carrying capacity. Previous PCB design tips did not take these dependencies into account, but designers need to be aware of them when determining layout parameters. Many PCB track/via calculators are now available online. Designers are advised to consult the PCB manufacturer or layout engineer for these details after completing the schematic design.

Avoid Overheating

There are many factors that contribute to heat generation, such as the housing, airflow, etc., but this section focuses on exposed pads. Controllers with exposed pads, such as the LTC3533, ADP5304, ADP2386, ADP5054, etc., have lower thermal resistance if properly connected to the board. Generally speaking, if the power MOSFET of the controller IC is placed in the die (i.e., it is monolithic), the pads of the IC are usually exposed to dissipate heat. If the converter IC is running with an external power MOSFET (a controller IC), then the controller IC generally does not need an exposed pad because its primary source of heat (the power MOSFET) is external to the IC itself.

Typically, these exposed pads must be soldered to the PCB ground plane to be effective. There are some exceptions depending on the IC, and some controllers will specify that they can be connected to an isolated pad PCB area to act as a heat sink for heat dissipation. If you are unsure, refer to the datasheet for the part in question.

When you connect the exposed pad to a PCB plane or isolated area, (a) make sure to connect the vias (many in an array) to the ground plane for heat dissipation (heat transfer). For multi-layer PCB ground planes, it is recommended to connect the ground planes on all layers below the pad with vias.

Note that this discussion of exposed pads is related to controllers. Using exposed pads in other ICs may require very different treatments.

Conclusion and Summary

Designing a low-noise power supply that does not affect system circuits due to burned-out rails or vias is a challenge in terms of cost, efficiency, efficiency, and PCB area. This article highlights some areas that designers may overlook, such as using power budget analysis to build a power tree to support all downstream loads.

Schematics and simulations are only the first step in the design, followed by careful device positioning and routing techniques. Vias, rails, and current carrying capabilities must all meet requirements and be evaluated. If switching noise is present at the interface location or reaches the power pins of the IC, the system circuit will malfunction and be difficult to isolate and troubleshoot.