Common PCB Layout Pitfalls

This article lists various design oversights, explores why each misstep can cause circuit failure, and gives suggestions on how to avoid these design flaws. This article uses a two-layer PCB with FR-4 dielectric and 0.0625in thickness as an example, with the bottom layer of the board grounded. The operating frequency is between 315MHz and 915MHz in different frequency bands, and the Tx and Rx powers are between -120dBm and +13dBm.

Inductor Direction

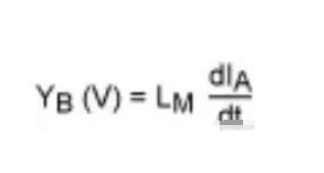

When two inductors (or even two PCB traces) are close to each other, mutual inductance will occur. The magnetic field generated by the current in the first circuit will excite the current in the second circuit (Figure 1). This process is similar to the mutual influence between the primary and secondary coils of a transformer. When the two currents interact through the magnetic field, the voltage generated is determined by the mutual inductance LM:

Where YB is the error voltage injected into circuit B, and IA is the current acting in circuit A1. LM is very sensitive to the circuit spacing, the inductor loop area (i.e., magnetic flux), and the loop direction. Therefore, the best balance between compact circuit layout and reduced coupling is to correctly arrange all inductors.

Figure 1. Magnetic lines of force

The magnetic lines of force in Figure 1 show that mutual inductance is related to the direction of inductor arrangement.

Adjust the direction of circuit B so that its current loop is parallel to the magnetic lines of force of circuit A. To achieve this goal, try to make the inductors perpendicular to each other.

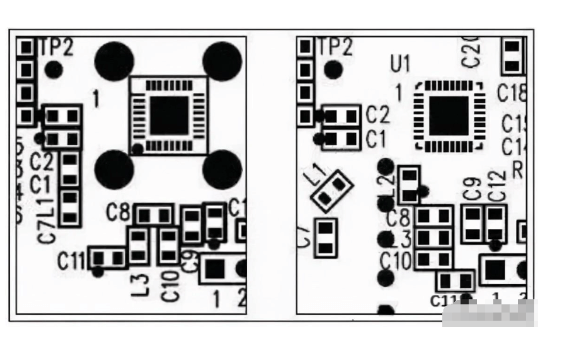

Figure 2. Two different PCB layouts

Figure 2 shows two different PCB layouts, one of which has unreasonable component arrangement direction (L1 and L3) and the other has a more appropriate arrangement direction.

The principles should be followed: the inductor spacing should be as far as possible; the inductor arrangement direction should be at right angles to minimize crosstalk between inductors.

Lead coupling

Just as the inductor arrangement direction affects magnetic field coupling, if the leads are too close to each other, it will also affect coupling. This layout problem also produces the so-called mutual inductance.

One of the most concerned issues in RF circuits is the routing of sensitive parts of the system, such as the input matching network, the resonant tank circuit of the receiver, and the antenna matching network of the transmitter.

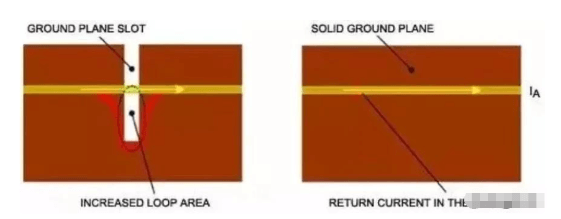

The return current path must be as close as possible to the main current path to minimize the radiated magnetic field. This layout helps reduce the current loop area.

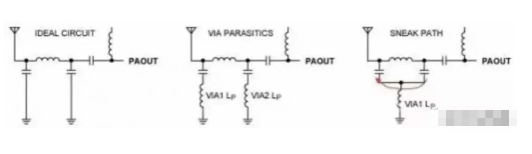

The ideal low-resistance path for the return current is usually the ground area under the lead—effectively limiting the loop area to the area of the dielectric thickness multiplied by the lead length. However, if the ground area is split, the loop area will increase (Figure 3). For leads that pass through the split area, the return current will be forced to pass through the high-resistance path, greatly increasing the current loop area. This layout also makes the circuit leads more susceptible to mutual inductance.

Figure 3. Complete large-area grounding helps improve system performance

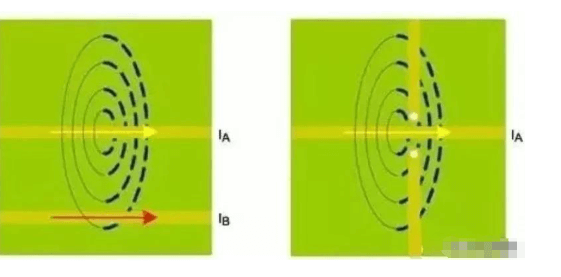

For a real inductor, the direction of the leads also has a great impact on magnetic field coupling. If the leads of the sensitive circuit must be close to each other, it is best to arrange the leads vertically to reduce coupling (Figure 4). If vertical arrangement is not possible, consider using a guard line.

Figure 4. Possible magnetic field line coupling

The principle should be followed: complete grounding should be ensured under the leads; sensitive leads should be arranged vertically; if the leads must be arranged in parallel, sufficient spacing must be ensured or a guard line should be used.

Ground vias

The main problem with RF circuit layout is usually the non-ideal characteristic impedance of the circuit, including circuit components and their interconnections. If the copper layer of the lead is thin, it is equivalent to an inductor line and forms a distributed capacitance with other adjacent leads. When the lead passes through the via, it will also show inductance and capacitance characteristics.

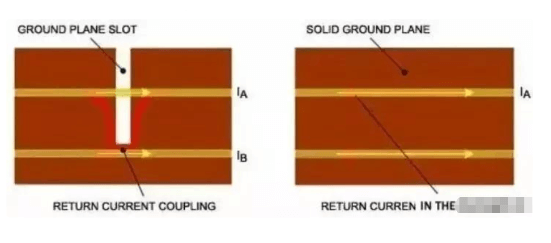

The capacitance of the via mainly comes from the capacitance between the copper on the side of the via pad and the copper on the ground layer, which are separated by a relatively small ring. Another influence comes from the cylinder of the metal via itself. The influence of parasitic capacitance is generally small and usually only causes the edge of high-speed digital signals to deteriorate.

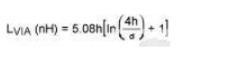

The biggest impact of the via is the parasitic inductance caused by the corresponding interconnection method. Because most metal vias in RF PCB design are the same size as the lumped component, a simple formula can be used to estimate the impact of circuit vias (Figure 5):

Where, LVIA is the lumped inductance of the via; h is the via height in inches; d is the via diameter in inches2.

Figure 5. PCB cross section of via structure used to estimate parasitic effects

Parasitic inductance often has a great impact on the connection of bypass capacitors. Ideal bypass capacitors provide high-frequency short circuits between the power layer and the ground layer, but non-ideal vias affect the low-inductance path between the ground layer and the power layer. A typical PCB via (d=10mil, h=62.5mil) is approximately equivalent to a 1.34nH inductor.

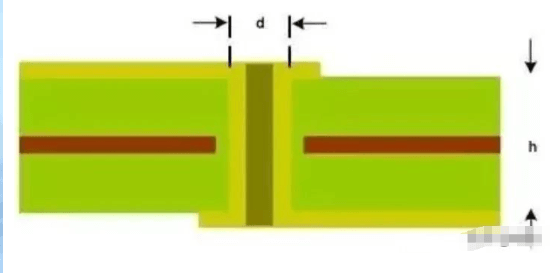

If sensitive circuits share vias, such as the two arms of a π-type network, other problems will arise. For example, placing an ideal via equivalent to a lumped inductor will result in a significant difference in the equivalent schematic from the original circuit design (Figure 6). Similar to crosstalk in shared current paths3, this leads to increased mutual inductance, increased crosstalk and feedthrough.

Figure 6. Ideal vs. non-ideal architecture

Figure 6 compares ideal vs. non-ideal architectures, with potential “signal paths” in the circuit.

The principles should be followed: ensure that the via inductance in sensitive areas is modeled; use independent vias for filters or matching networks; thinner PCB copper will reduce the impact of via parasitic inductance.

Grounding and filling

The ground or power layer defines a common reference voltage and supplies power to all parts of the system through a low-resistance path. In this way, all electric fields are balanced and a good shielding mechanism is produced.

DC current always tends to flow along a low-resistance path. Similarly, high-frequency current also prefers to flow through the path with the lowest resistance. Therefore, for a standard PCB microstrip line above the ground layer, the return current tries to flow into the ground area just below the lead. As described in the lead coupling section above, the cut ground area will introduce various noises, which will increase crosstalk by magnetic field coupling or current convergence (Figure 7).

Figure 7. Keep the ground layer intact as much as possible, otherwise the return current will cause crosstalk

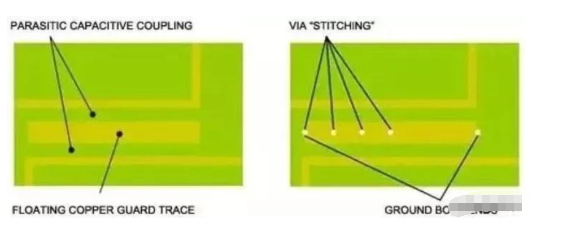

Filling ground is also called a guard line. It is usually used in designs where it is difficult to lay a continuous ground area in the circuit or where sensitive circuits need to be shielded (Figure 8). The shielding effect is increased by placing ground vias (i.e., via arrays) at both ends of the lead or along the line. Do not mix guard traces with traces designed to provide return current paths, as this layout will introduce crosstalk.

Figure 8. Avoid floating copper traces in RF system design, especially when copper foil is required

When a copper area is not grounded (floating) or is only grounded at one end, it will limit its effectiveness. In some cases, it will form parasitic capacitance, change the impedance of surrounding wiring, or create a “latent” path between circuits, which will cause adverse effects. In short, if a copper area is laid on the circuit board (non-circuit signal traces), ensure consistent plating thickness. Floating copper areas should be avoided because they will affect the circuit design.

Finally, make sure to consider the impact of any ground areas near the antenna. Any monopole antenna uses ground areas, traces and vias as part of the system balance, and non-ideal balanced routing will affect the radiation efficiency and direction (radiation pattern) of the antenna. Therefore, the ground area should not be placed directly under the monopole PCB lead antenna.

The principles should be followed: try to provide a continuous, low-resistance grounding area; ground both ends of the fill line, and use a via array as much as possible; do not float the copper wire near the RF circuit, and do not lay copper foil around the RF circuit; if the circuit board includes multiple ground layers, it is best to lay a ground via when the signal line passes from one side to the other.