Distinguishing High-Speed and Low-Speed Signals in PCB Design

Introduction

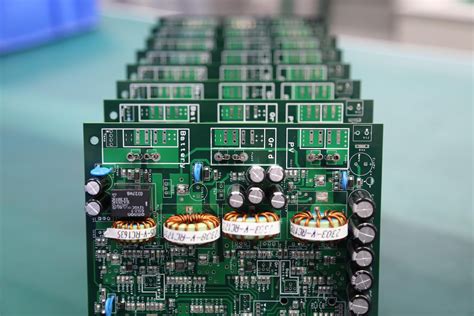

Printed Circuit Board (PCB) design involves managing various types of signals, including high-speed and low-speed signals. Properly distinguishing between these signals is crucial for ensuring signal integrity, minimizing electromagnetic interference (EMI), and optimizing overall circuit performance. This article explores the key differences between high-speed and low-speed signals, their impact on PCB design, and best practices for handling them effectively.

1. Understanding Signal Speed in PCB Design

Before distinguishing between high-speed and low-speed signals, it is essential to define what constitutes signal speed in PCB design. Signal speed is not solely determined by clock frequency but also by signal rise time, edge rate, and propagation delay.

1.1 Key Parameters Affecting Signal Classification

- Clock Frequency (f): The periodic rate at which a signal switches (e.g., 1 MHz vs. 1 GHz).

- Rise Time (tr) and Fall Time (tf): The time taken for a signal to transition from 10% to 90% of its maximum amplitude. Fast rise times (e.g., <1 ns) are typical in high-speed signals.

- Signal Edge Rate (dV/dt): The rate of voltage change over time, which affects EMI and crosstalk.

- Propagation Delay: The time taken for a signal to travel from the transmitter to the receiver.

1.2 Defining High-Speed vs. Low-Speed Signals

- Low-Speed Signals:

- Typically operate at frequencies below 50 MHz.

- Have slow rise/fall times (>10 ns).

- Examples: GPIO, UART, I2C, and basic control signals.

- High-Speed Signals:

- Operate at frequencies above 50 MHz (or even GHz range).

- Have fast rise/fall times (<1 ns).

- Examples: DDR memory, PCIe, USB 3.0, HDMI, and RF signals.

A signal may also be considered high-speed if its edge rate causes transmission line effects, even if its frequency is low.

2. Transmission Line Effects and Signal Integrity

High-speed signals behave differently from low-speed signals due to transmission line effects. When the signal wavelength becomes comparable to the trace length, impedance mismatches, reflections, and signal degradation become significant concerns.

2.1 Critical Length for High-Speed Signals

The critical length (Lcrit) determines whether a signal requires transmission line treatment:

[

L_{crit} = \frac{t_r \times c}{2 \times \sqrt{\varepsilon_r}}

]

Where:

- ( t_r ) = rise time

- ( c ) = speed of light (~3×108 m/s)

- ( \varepsilon_r ) = dielectric constant of the PCB material

If the trace length exceeds ( L_{crit}/6 ), the signal should be treated as high-speed.

2.2 Signal Integrity Challenges in High-Speed Design

- Reflections: Caused by impedance mismatches at connectors, vias, or load mismatches.

- Crosstalk: High-speed signals induce electromagnetic coupling in adjacent traces.

- Ground Bounce: Fast switching causes power/ground plane noise.

- Skin Effect: At high frequencies, current flows near the conductor surface, increasing resistance.

Low-speed signals are less susceptible to these issues but may still require basic noise mitigation.

3. Design Considerations for High-Speed vs. Low-Speed Signals

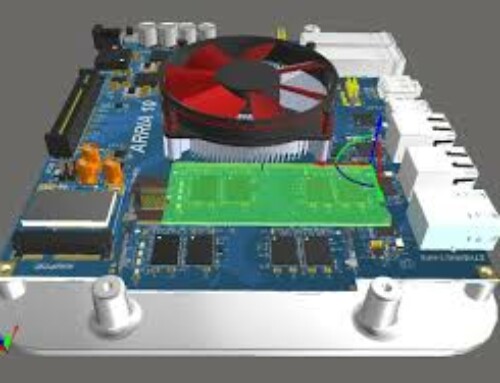

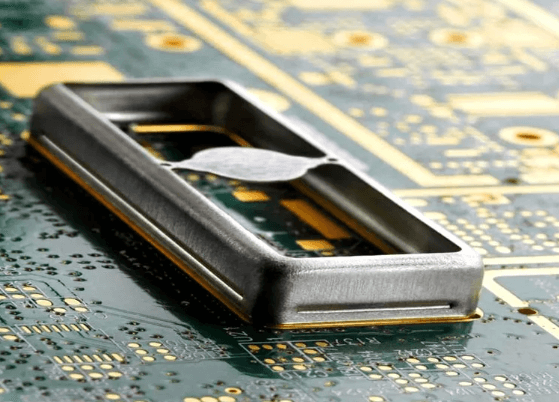

3.1 PCB Stackup and Layer Planning

- High-Speed Signals:

- Use controlled impedance traces (e.g., microstrip or stripline).

- Route signals adjacent to solid ground planes to minimize loop inductance.

- Avoid splitting reference planes beneath high-speed traces.

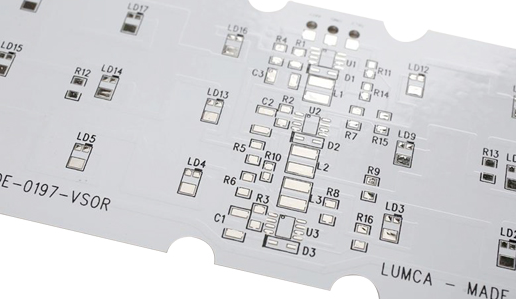

- Low-Speed Signals:

- Can be routed on outer layers without strict impedance control.

- Less sensitive to return path discontinuities.

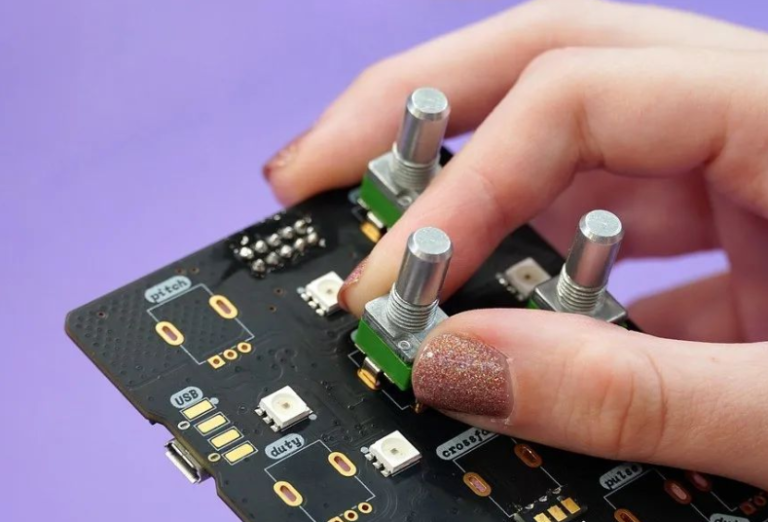

3.2 Trace Routing and Termination

- High-Speed Routing Best Practices:

- Minimize sharp bends (use 45° or curved traces).

- Match trace lengths for differential pairs (e.g., USB, PCIe).

- Use termination resistors (series or parallel) to reduce reflections.

- Low-Speed Routing:

- Basic routing rules apply (avoid excessive stubs, maintain reasonable spacing).

- Termination is rarely needed unless dealing with long cables.

3.3 Power Integrity and Decoupling

- High-Speed Circuits:

- Require low-inductance decoupling capacitors near ICs.

- Use multiple power/ground vias to reduce impedance.

- Low-Speed Circuits:

- Standard decoupling (e.g., 0.1 µF capacitors) is usually sufficient.

3.4 EMI and Shielding Techniques

- High-Speed Signals:

- Use guard traces or ground shielding to reduce crosstalk.

- Follow the 3W rule (spacing ≥ 3× trace width) to minimize coupling.

- Low-Speed Signals:

- Basic spacing rules apply, but EMI is less critical.

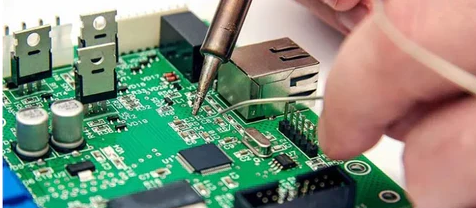

4. Simulation and Testing for Signal Validation

To ensure proper signal behavior, engineers use:

- Time-Domain Reflectometry (TDR): Measures impedance variations.

- Eye Diagram Analysis: Evaluates signal integrity in high-speed links.

- SPICE Simulations: Predict signal behavior before fabrication.

Low-speed signals typically require minimal simulation unless operating in noisy environments.

5. Conclusion

Distinguishing between high-speed and low-speed signals is vital for successful PCB design. High-speed signals demand controlled impedance, careful routing, and termination to maintain signal integrity, while low-speed signals follow simpler design rules. By understanding the key differences and applying best practices, designers can optimize performance, reduce EMI, and ensure reliable circuit operation.