Highly Accelerated Life Testing (HALT) for Printed Circuit Boards (PCBs): A Comprehensive Guide

Introduction to HALT for PCBs

Highly Accelerated Life Testing (HALT) has emerged as a critical methodology in the electronics industry for evaluating the reliability and robustness of Printed Circuit Boards (PCBs) and their assemblies. This accelerated stress testing approach goes beyond traditional testing methods by subjecting products to extreme environmental conditions to rapidly identify potential failure modes and design weaknesses.

In today’s competitive electronics market, where product life cycles are shrinking and reliability expectations are increasing, HALT provides manufacturers with a powerful tool to enhance product durability while reducing time-to-market. For PCBs, which form the foundation of nearly all electronic devices, HALT offers invaluable insights into how boards will perform under stressful conditions throughout their operational lifespan.

The Fundamentals of HALT Methodology

HALT represents a paradigm shift from conventional reliability testing approaches. Unlike qualification tests that verify whether a product meets specified requirements, HALT is an exploratory process designed to push products beyond their specified limits to uncover failure mechanisms.

The core philosophy of HALT revolves around three key principles:

- Accelerated Stress Testing: Applying stresses far beyond normal operating conditions to rapidly precipitate failures

- Failure Mode Discovery: Identifying all possible failure modes rather than just verifying compliance

- Design Margins Exploration: Determining the operational and destruct limits of the product

For PCBs, this typically involves subjecting boards to progressively increasing levels of thermal cycling, vibration, electrical stress, and combined environments. The process continues until fundamental limits of the technology are reached, providing engineers with crucial data about the board’s robustness.

Key Stress Factors in PCB HALT

Thermal Stress Testing

Thermal cycling forms one of the most critical components of PCB HALT. The process involves rapidly alternating between extreme high and low temperatures, often ranging from -100°C to +200°C. This thermal shock testing reveals several potential PCB weaknesses:

- CTE Mismatch Failures: Differences in coefficients of thermal expansion between PCB materials (laminate, copper, components) can cause cracking or delamination

- Solder Joint Fatigue: Repeated thermal cycling accelerates solder joint degradation, predicting long-term reliability issues

- Material Degradation: Extreme temperatures can cause PCB substrate materials to break down prematurely

- Plated Through-Hole Reliability: Thermal cycling stresses the connections between layers in multilayer boards

Vibration Stress Testing

Random vibration testing in HALT exposes PCBs to multi-axis vibration with progressively increasing intensity. This helps identify:

- Mechanical Weak Points: Components with inadequate mechanical support or mounting

- Solder Joint Integrity: Vibration-induced failures in solder connections

- Resonant Frequencies: Board natural frequencies that could lead to operational failures

- Connector Reliability: Intermittent connections caused by vibration

Combined Environmental Stress Testing

The most revealing HALT results often come from combining multiple stress factors simultaneously. Typical combinations include:

- Thermal cycling with vibration

- Temperature extremes with power cycling

- Humidity with electrical stress

These combined environments often uncover failure modes that wouldn’t appear under single stress conditions, better simulating real-world operating environments.

The HALT Process for PCBs

A structured approach to PCB HALT ensures comprehensive results while maintaining test efficiency:

1. Pretest Preparation

- Sample Selection: Choosing representative production samples

- Fixture Design: Creating appropriate mounting fixtures that don’t artificially strengthen the PCB

- Instrumentation: Installing sensors and data acquisition systems

- Functional Testing: Establishing baseline performance metrics

2. Step Stress Testing

The core HALT methodology involves applying stresses in incremental steps:

Thermal Step Stress:

- Start at product specification limits

- Increase in 10°C increments

- Hold at each step for sufficient time to reach thermal equilibrium

- Perform functional testing at each step

- Continue until destruction limit is found

Vibration Step Stress:

- Begin at 5-10 Grms (root mean square acceleration)

- Increase in 5 Grms increments

- Perform functional monitoring throughout

- Continue until destruct limit is identified

3. Failure Analysis

When failures occur:

- Document exact stress conditions

- Analyze failure mechanisms

- Determine if failure represents a design weakness

- Classify as operational limit or destruct limit

4. Corrective Actions

Based on findings:

- Implement design improvements

- Modify material selections

- Change manufacturing processes

- Update component specifications

5. Verification Testing

Repeat HALT on improved designs to verify enhanced robustness

Advantages of HALT for PCB Development

The implementation of HALT in PCB development offers numerous benefits:

Accelerated Reliability Assessment

HALT condenses months or years of field operation into days or weeks of testing, providing rapid feedback for design iterations.

Comprehensive Failure Mode Discovery

By pushing boards beyond normal limits, HALT reveals failure modes that might otherwise only appear after prolonged field use.

Improved Design Margins

HALT quantifies the actual safety margins in PCB designs, allowing engineers to optimize robustness without excessive overdesign.

Reduced Time-to-Market

Early identification and correction of reliability issues prevents costly redesigns later in the product development cycle.

Cost Savings

Finding and fixing problems during development is far less expensive than field failures and recalls.

Competitive Advantage

Products developed with HALT typically demonstrate superior field reliability, enhancing brand reputation.

Challenges and Limitations of PCB HALT

While highly valuable, HALT does present certain challenges:

Equipment Requirements

HALT chambers capable of rapid thermal cycling and multi-axis vibration represent significant capital investments.

Test Interpretation

Distinguishing between realistic failure modes and artificial test-induced failures requires experienced analysis.

Sample Size Considerations

Limited sample sizes in HALT may miss some low-probability failure modes.

Correlation to Real-World Use

While HALT accelerates failure mechanisms, correlating results to actual field life requires careful analysis.

Destructive Nature

HALT typically continues until failure, requiring multiple test samples.

Best Practices for Effective PCB HALT Implementation

To maximize the value of HALT for PCB development, consider these best practices:

Early Implementation

Incorporate HALT as early as possible in the design cycle when changes are easier and less costly to implement.

Representative Samples

Ensure test samples accurately reflect production intent designs and manufacturing processes.

Comprehensive Monitoring

Implement thorough electrical monitoring to detect intermittent failures and performance degradation.

Cross-Functional Teams

Include design, manufacturing, and reliability engineers in test planning and analysis.

Documentation Rigor

Maintain detailed records of all test parameters, observations, and failure analyses.

Iterative Testing

Conduct multiple HALT cycles as designs evolve to verify improvements.

Case Studies: HALT in PCB Applications

Automotive Electronics

A tier-1 automotive supplier implemented HALT on engine control modules, discovering:

- Solder joint cracks at -45°C (below specified operating limit)

- Connector fretting at 18 Grms vibration

Redesigns prior to production prevented potential field failures in extreme climates.

Aerospace Avionics

HALT on flight control PCBs revealed:

- Delamination of high-Tg materials at 175°C

- Resonant vibration failures at 32 Grms

Findings led to material changes and additional mounting points.

Consumer Electronics

A smartphone manufacturer used HALT to:

- Identify BGA solder fatigue issues

- Optimize underfill material selection

- Reduce field failure rates by 60%

Future Trends in PCB HALT

Emerging developments in HALT methodology include:

Advanced Simulation Integration

Combining physical HALT with virtual reliability simulations for more comprehensive analysis.

IoT-Enabled Monitoring

Wireless sensors and IoT technologies enabling more comprehensive real-time performance monitoring during HALT.

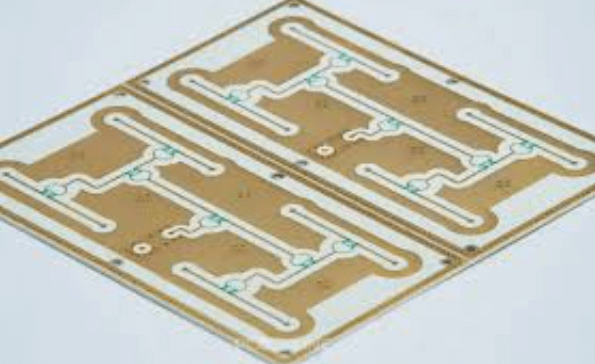

Materials-Specific HALT Protocols

Developing specialized HALT approaches for new PCB materials like flexible circuits and high-frequency laminates.

AI-Assisted Failure Analysis

Machine learning algorithms to predict failure modes from HALT data patterns.

Conclusion

Highly Accelerated Life Testing has become an indispensable tool in the development of reliable, robust printed circuit boards. By aggressively stressing PCBs beyond their normal operating limits, HALT uncovers potential failure modes early in the design process when they are most cost-effective to address. The methodology provides invaluable data about the true margins of safety in PCB designs, enabling engineers to optimize both performance and reliability.

As electronic devices continue to proliferate in increasingly demanding environments, from automotive to aerospace to industrial applications, the importance of thorough reliability testing only grows. HALT represents one of the most effective approaches to ensure PCB designs meet these challenges while maintaining aggressive development schedules.

For organizations committed to delivering high-reliability electronic products, investment in HALT capabilities and expertise yields significant returns in reduced warranty costs, enhanced brand reputation, and superior product performance. By incorporating HALT into the standard PCB development workflow, manufacturers can achieve new levels of quality and reliability in their electronic products.