How to Reduce Ground Bounce in PCB Design

Introduction

Ground bounce is one of the most challenging signal integrity issues in modern high-speed printed circuit board (PCB) designs. As clock frequencies increase and signal rise times become faster, ground bounce has emerged as a critical factor limiting system performance and reliability. This phenomenon occurs when transient currents flowing through the parasitic inductance of ground connections cause momentary shifts in the ground reference voltage. These voltage fluctuations can lead to false switching, timing errors, increased electromagnetic interference (EMI), and overall degradation of system performance.

This article provides a comprehensive examination of ground bounce in PCBs, exploring its fundamental causes, measurement techniques, and most importantly, practical design strategies to minimize its impact. By implementing these techniques, engineers can significantly improve signal integrity and reduce noise-related issues in their PCB designs.

Understanding Ground Bounce

Definition and Physics of Ground Bounce

Ground bounce refers to the voltage fluctuation that occurs in a ground reference when current flows through the parasitic inductance associated with ground connections. The basic physics follows the fundamental relationship:

V = L × (di/dt)

Where:

- V is the ground bounce voltage

- L is the parasitic inductance

- di/dt is the rate of change of current

When multiple output drivers switch simultaneously, the rapid current changes (high di/dt) through the finite inductance of package leads and PCB traces create these unwanted voltage spikes in the ground reference.

Primary Causes of Ground Bounce

Several factors contribute to ground bounce in PCB designs:

- Parasitic Inductance: All real-world conductors have some inductance, and ground connections are no exception. This includes bond wires, package leads, vias, and PCB traces.

- Simultaneous Switching Outputs (SSO): When multiple output drivers change state at the same time, their combined current demands create larger ground disturbances.

- Fast Edge Rates: Modern digital circuits with sub-nanosecond rise times produce very high di/dt values, exacerbating ground bounce effects.

- Poor Return Path Design: Discontinuous or high-impedance return paths force current to take longer routes, increasing loop inductance.

- Inadequate Decoupling: Insufficient or improperly placed decoupling capacitors fail to provide the instantaneous current needed during switching transitions.

Measurement and Analysis Techniques

Identifying Ground Bounce

Ground bounce manifests in several observable ways:

- Increased jitter in clock signals

- False triggering of logic gates

- Reduced noise margins

- Intermittent system failures

- Radiated EMI problems

Measurement Methods

Several techniques exist for measuring ground bounce:

- Oscilloscope Measurements: Using high-bandwidth oscilloscopes with proper grounding techniques to directly observe ground disturbances.

- Time Domain Reflectometry (TDR): Helps characterize impedance discontinuities in ground paths.

- Vector Network Analyzer (VNA) Measurements: For analyzing ground impedance across frequency.

- Near-field Probes: Useful for identifying localized ground bounce hotspots.

Simulation Approaches

Modern PCB design tools offer various simulation methods to predict ground bounce:

- SPICE Simulations: Can model simple ground bounce scenarios with lumped elements.

- 3D Electromagnetic Field Solvers: Provide more accurate modeling of distributed parasitic effects.

- Signal Integrity Analysis Tools: Specialized software for analyzing simultaneous switching noise.

Design Techniques to Reduce Ground Bounce

1. Optimize PCB Layer Stackup

A well-designed layer stack is fundamental to controlling ground bounce:

- Dedicated Ground Planes: Use continuous, unbroken ground planes to provide low-impedance return paths.

- Thin Dielectrics: Place signal layers close to their adjacent ground planes to minimize loop area.

- Multiple Ground Layers: In complex designs, use multiple ground layers connected with numerous vias.

- Symmetrical Stackup: Helps balance capacitive coupling and reduce mode conversion.

2. Implement Proper Decoupling Strategies

Effective decoupling is crucial for managing ground bounce:

- Use Multiple Capacitor Values: Combine bulk, ceramic, and high-frequency capacitors to cover different frequency ranges.

- Placement Close to ICs: Position decoupling capacitors as near as possible to power pins.

- Low-ESL Capacitors: Select capacitors with low equivalent series inductance (ESL).

- Interplane Capacitance: Utilize the natural capacitance between power and ground planes.

3. Manage Simultaneous Switching Outputs

Reducing SSO effects can significantly lower ground bounce:

- Stagger Switching Times: When possible, design circuits to avoid all outputs switching simultaneously.

- Use Gradual Turn-on Circuits: Implement slew rate control for output drivers.

- Distribute Drivers: Physically separate output drivers to reduce concentrated current demands.

- Current Limiting: Consider resistors or other means to limit peak switching currents.

4. Optimize Component Selection and Placement

Thoughtful component choices and placement can mitigate ground bounce:

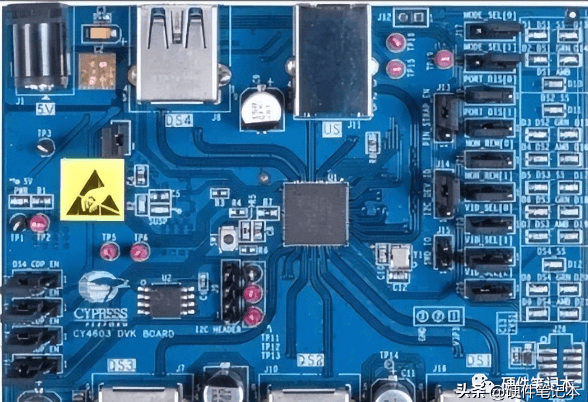

- Low-Inductance Packages: Prefer packages with multiple ground pins (e.g., BGA over QFP).

- Short Bond Wires: Select ICs with minimal internal ground path inductance.

- Proper Pin Assignment: Group ground pins near high-current output pins.

- Minimize Lead Lengths: Keep component leads and PCB traces as short as possible.

5. Improve Grounding Techniques

Advanced grounding methods can reduce ground impedance:

- Multi-point Grounding: For mixed-signal designs, carefully implement multi-point grounding strategies.

- Ground Via Arrays: Use numerous closely-spaced vias to connect ground layers.

- Ground Stitching: Place ground vias around the perimeter and at regular intervals across the board.

- Separate Analog and Digital Grounds: With proper single-point connection when needed.

6. Signal Integrity Considerations

Proper signal routing affects ground bounce:

- Controlled Impedance Routing: Match trace impedances to prevent reflections.

- Minimize Loop Areas: Keep signal paths close to their return paths.

- Avoid Ground Plane Splits: Don’t route high-speed signals over gaps in ground planes.

- Differential Signaling: Where applicable, use differential pairs for better noise immunity.

7. Power Delivery Network (PDN) Optimization

A robust PDN helps minimize ground bounce:

- Low-Impedance Power Distribution: Design the PDN to have minimal impedance across the relevant frequency range.

- Proper Plane Capacitance: Ensure adequate capacitance between power and ground planes.

- PDN Analysis: Perform frequency-domain analysis of the power delivery network.

- Voltage Regulator Placement: Position regulators close to their loads with proper bypassing.

Advanced Techniques for High-Speed Designs

For particularly challenging high-speed designs, consider these advanced methods:

- Embedded Capacitance: Use materials with high dielectric constant between power and ground planes to create distributed capacitance.

- On-Die Decoupling: Utilize the intrinsic capacitance of the semiconductor device itself.

- Active Cancellation Techniques: Implement circuits that actively counteract ground bounce effects.

- Spread Spectrum Clocking: Reduce peak spectral content by dithering the clock frequency.

- Optimal Termination Strategies: Properly terminate transmission lines to minimize reflections.

Verification and Testing

After implementing ground bounce reduction techniques, verification is essential:

- Prototype Testing: Measure actual ground bounce on physical prototypes under various operating conditions.

- Correlation with Simulation: Compare measured results with pre-layout simulations to improve modeling accuracy.

- Design Iteration: Be prepared to make adjustments based on test results.

- Corner Case Testing: Verify performance under extreme temperature, voltage, and loading conditions.

Conclusion

Ground bounce presents a significant challenge in modern PCB design, but through careful implementation of proper design techniques, its effects can be substantially reduced. The key approaches include optimizing the PCB stackup, implementing effective decoupling strategies, managing simultaneous switching outputs, selecting appropriate components, improving grounding methods, maintaining signal integrity, and optimizing the power delivery network.

As digital systems continue to push toward higher speeds and greater complexity, understanding and mitigating ground bounce becomes increasingly critical. By applying the principles outlined in this article, designers can create PCBs that deliver reliable performance while minimizing ground bounce-related issues. The most effective designs often combine multiple techniques tailored to the specific requirements of each application.

Remember that ground bounce reduction is not a one-time task but rather an ongoing consideration throughout the entire design process—from initial concept through final validation. With careful attention to these details, engineers can successfully navigate the challenges posed by ground bounce in their PCB designs.