How to Reduce Parasitic Capacitance in PCB Layout

Introduction

Parasitic capacitance is an unavoidable phenomenon in printed circuit board (PCB) design that can negatively impact signal integrity, increase crosstalk, and degrade high-frequency performance. As electronic devices operate at increasingly higher speeds, managing parasitic capacitance becomes crucial to ensure reliable circuit performance. This article explores the causes of parasitic capacitance in PCB layouts and provides practical strategies to minimize its effects.

1. Understanding Parasitic Capacitance

1.1 Definition of Parasitic Capacitance

Parasitic capacitance refers to the unintentional capacitance that exists between conductors (traces, pads, or planes) due to their proximity and the dielectric properties of the PCB material. Unlike intentional capacitors designed into a circuit, parasitic capacitance is an unwanted side effect that can lead to signal distortion, delays, and electromagnetic interference (EMI).

1.2 How Parasitic Capacitance Forms

Parasitic capacitance arises when two conductive elements are separated by an insulating material (dielectric). The capacitance (C) can be approximated by the parallel-plate capacitor formula:

[C = \frac{\varepsilon_r \varepsilon_0 A}{d}]

Where:

- ( \varepsilon_r ) = Relative permittivity of the dielectric material

- ( \varepsilon_0 ) = Permittivity of free space (8.854 × 10⁻¹² F/m)

- ( A ) = Overlapping area between conductors

- ( d ) = Distance between conductors

From this equation, we see that parasitic capacitance increases with:

- Larger overlapping conductor areas (( A ))

- Higher dielectric constant (( \varepsilon_r ))

- Smaller separation distance (( d ))

2. Effects of Parasitic Capacitance in PCBs

Excessive parasitic capacitance can lead to several issues, including:

- Signal Integrity Degradation: Slows down edge rates, causing signal delays and reflections.

- Increased Crosstalk: Coupling between adjacent traces introduces noise.

- Reduced Bandwidth: Limits high-frequency performance in RF and high-speed digital circuits.

- Power Loss: Energy is wasted in charging and discharging parasitic capacitances.

To mitigate these effects, PCB designers must adopt layout techniques that minimize parasitic capacitance.

3. Strategies to Reduce Parasitic Capacitance

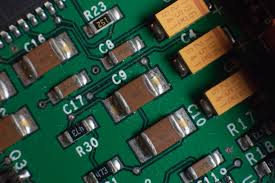

3.1 Optimize Trace Geometry

- Minimize Trace Width: Narrower traces reduce the overlapping area (( A )) with adjacent conductors.

- Use Microstrip or Stripline Configurations: Controlled impedance traces with proper reference planes help manage capacitance.

- Avoid Long Parallel Traces: Long adjacent traces increase capacitive coupling. Stagger traces or route them orthogonally on different layers.

3.2 Increase Spacing Between Conductors

- Follow the 3W Rule: Keep traces at least three times the trace width (( 3W )) apart to reduce crosstalk.

- Separate High-Speed Signals: Sensitive signals (e.g., clock lines) should have extra spacing from noisy traces.

3.3 Choose Low-Dielectric Constant Materials

- Use PCB Substrates with Low ( \varepsilon_r ): Materials like Rogers or PTFE-based laminates have lower dielectric constants than standard FR4, reducing parasitic capacitance.

- Avoid High-( \varepsilon_r ) Solder Masks: Some solder mask materials increase capacitance; select low-( \varepsilon_r ) options where possible.

3.4 Reduce Overlapping Conductors

- Avoid Large Ground Pads Under High-Speed Signals: Large copper pours beneath signal traces increase capacitance.

- Use Split Planes Carefully: Ensure power and ground planes do not create unintended capacitive coupling.

3.5 Implement Proper Layer Stackup

- Increase Dielectric Thickness: A thicker dielectric layer (( d )) between signal and reference planes reduces capacitance.

- Use Buried or Blind Vias: These minimize via stub effects, which can introduce parasitic capacitance.

3.6 Minimize Via Stubs

- Use Back-Drilling: Removes unused via portions to reduce stub capacitance.

- Optimize Via Aspect Ratio: Shorter vias with smaller diameters reduce parasitic effects.

3.7 Guard Traces and Shielding

- Insert Guard Traces: Grounded traces between sensitive signals reduce capacitive coupling.

- Use Shielding Techniques: Enclose high-frequency traces in grounded copper to prevent external interference.

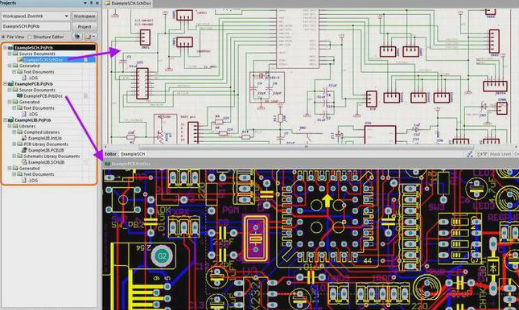

3.8 Simulation and Analysis

- Perform Parasitic Extraction: Use tools like Ansys SIwave, Cadence Sigrity, or Altium to model and minimize parasitic capacitance.

- Time-Domain Reflectometry (TDR): Helps identify impedance mismatches caused by excessive capacitance.

4. Practical Examples of Parasitic Capacitance Reduction

4.1 High-Speed Digital Design

- Differential Pair Routing: Ensures balanced capacitance between pairs, reducing skew.

- Length Matching: Prevents timing issues caused by uneven parasitic capacitance.

4.2 RF and Microwave PCBs

- Minimize Stray Capacitance in Filters: Properly space inductor and capacitor components.

- Use Coplanar Waveguides: Reduces parasitic effects compared to microstrip lines.

4.3 Mixed-Signal Layouts

- Separate Analog and Digital Grounds: Prevents capacitive coupling between noisy and sensitive circuits.

- Star Grounding: Reduces ground loops and associated parasitic capacitance.

5. Conclusion

Parasitic capacitance is an inherent challenge in PCB design, but its impact can be significantly reduced through careful layout practices. By optimizing trace geometry, increasing conductor spacing, selecting appropriate materials, and leveraging simulation tools, designers can enhance signal integrity and ensure reliable circuit operation—especially in high-frequency and high-speed applications. Implementing these strategies will lead to more efficient, noise-resistant PCBs capable of meeting modern electronic performance demands.