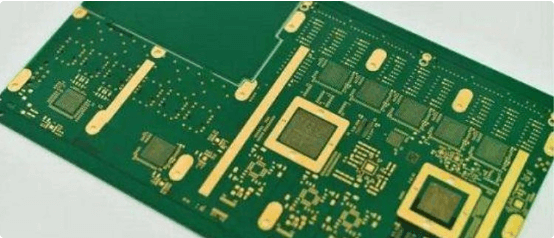

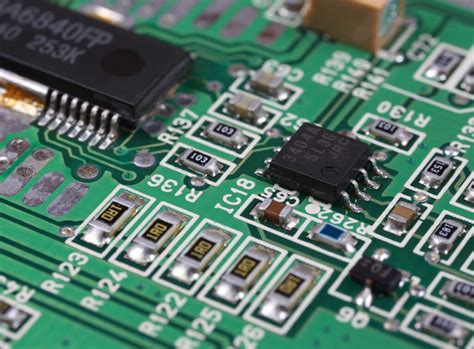

Key Considerations for High-Speed Multilayer PCB Design

Introduction

In today’s rapidly evolving electronics industry, high-speed multilayer printed circuit boards (PCBs) have become essential components in advanced electronic systems. From high-performance computing and telecommunications to aerospace and medical devices, these complex boards enable the high-frequency operation and miniaturization that modern technology demands. However, designing high-speed multilayer PCBs presents numerous challenges that require careful consideration to ensure signal integrity, power integrity, and electromagnetic compatibility. This article explores the critical issues designers must address when working with high-speed multilayer PCBs, providing practical insights for successful implementation.

1. Signal Integrity Considerations

1.1 Transmission Line Effects

At high frequencies, PCB traces behave as transmission lines rather than simple conductors. This transition typically occurs when trace lengths approach 1/10 of the signal wavelength. Designers must account for:

- Characteristic impedance: Maintain consistent impedance (typically 50Ω or 100Ω differential) throughout the signal path

- Impedance matching: Use proper termination techniques to prevent reflections

- Microstrip vs. stripline configurations: Choose appropriate trace routing based on speed and layer stackup

1.2 Crosstalk Mitigation

Electromagnetic coupling between adjacent traces can cause unwanted signal interference:

- Maintain adequate spacing (3× trace width minimum) between parallel traces

- Implement orthogonal routing on adjacent layers to minimize coupling

- Use guard traces or ground vias for critical signals

- Consider differential signaling for noise-sensitive high-speed interfaces

1.3 Signal Return Paths

High-frequency signals follow the path of least inductance, not necessarily the shortest physical path:

- Ensure uninterrupted ground planes beneath signal traces

- Avoid splitting planes under high-speed signals

- Place ground vias near signal vias to provide continuous return paths

- Be cautious of slots or gaps in reference planes

2. Power Integrity Management

2.1 Power Distribution Network (PDN) Design

A robust PDN is crucial for stable operation:

- Implement appropriate layer stacking with dedicated power and ground planes

- Use multiple vias for power connections to reduce inductance

- Consider the target impedance of the PDN (typically <1Ω up to GHz frequencies)

- Implement proper decoupling capacitor strategy:

- Use a mix of bulk, ceramic, and high-frequency capacitors

- Place capacitors close to power pins

- Consider interplane capacitance for very high-speed designs

2.2 Simultaneous Switching Noise (SSN)

Multiple devices switching simultaneously can cause ground bounce and power droop:

- Distribute ground connections evenly across the PCB

- Use separate power islands for noisy circuits

- Implement proper bypassing and decoupling

- Consider split ground planes carefully (only when necessary)

3. Layer Stackup Configuration

3.1 Optimal Layer Arrangement

A well-planned stackup is fundamental to successful high-speed design:

- Follow the “signal-ground-signal-power” sandwich pattern when possible

- Place high-speed signals between ground planes (stripline configuration) for better shielding

- Use symmetrical stackups to prevent warping

- Consider controlled impedance requirements when determining dielectric thicknesses

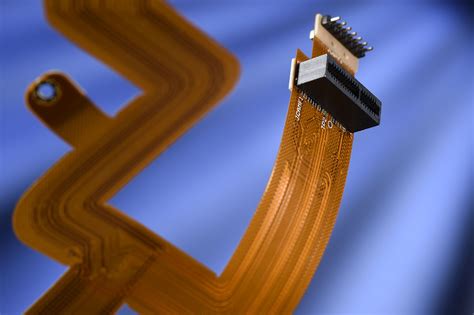

3.2 Material Selection

Standard FR-4 may not suffice for very high-speed designs:

- Consider low-loss materials (e.g., Rogers, Isola) for RF/high-speed digital layers

- Evaluate dielectric constant (Dk) and dissipation factor (Df) at operating frequencies

- Account for thermal expansion characteristics in multilayer designs

- Balance performance requirements with cost constraints

4. Electromagnetic Compatibility (EMC)

4.1 Radiation Control

High-speed designs can unintentionally become efficient antennas:

- Maintain proper grounding techniques throughout the design

- Implement shielding cans or conductive coatings when necessary

- Use stitching vias around board edges and between ground planes

- Consider the “20-H rule” for containing electromagnetic fields

4.2 Sensitive Circuit Protection

Shield vulnerable circuits from interference:

- Physically separate analog and digital sections

- Implement moats or bridges for sensitive areas when needed

- Use filtered power supplies for noise-sensitive components

- Consider the use of buried capacitance layers

5. Thermal Management

5.1 Heat Dissipation Considerations

High-speed designs often generate significant heat:

- Incorporate thermal vias under high-power components

- Distribute heat-generating components across the board

- Consider copper weight and plane layers for heat spreading

- Plan for adequate airflow or heatsinking in the final assembly

5.2 Thermal-Induced Stress

Multilayer boards are susceptible to thermal expansion issues:

- Balance copper distribution across layers

- Use symmetrical stackups to minimize warping

- Consider CTE (Coefficient of Thermal Expansion) matching for components and board materials

- Account for thermal gradients in large boards

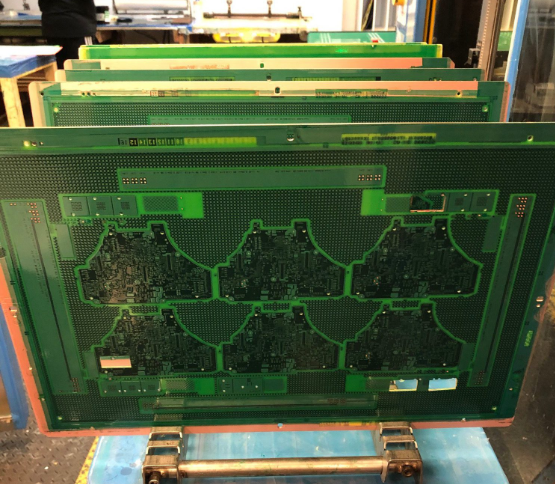

6. Manufacturing Considerations

6.1 Design for Manufacturability (DFM)

Complex multilayer boards push manufacturing capabilities:

- Consult with your PCB fabricator early in the design process

- Maintain appropriate clearance and spacing rules

- Consider aspect ratio limitations for vias and microvias

- Account for material tolerances in impedance calculations

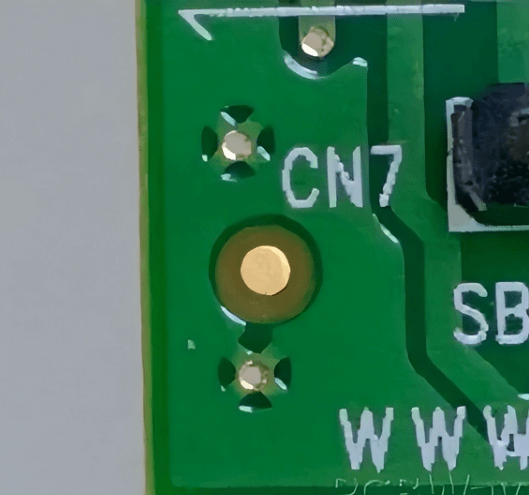

6.2 Via Selection and Placement

Via implementation significantly impacts high-speed performance:

- Use appropriate via types (through-hole, blind, buried, microvia)

- Minimize stub lengths (consider backdrilling for critical signals)

- Implement via shielding when necessary

- Consider via-in-pad techniques for dense designs

7. High-Speed Routing Techniques

7.1 Trace Routing Best Practices

- Route critical signals first with shortest possible paths

- Avoid sharp angles (use 45° or curved traces)

- Match trace lengths for timing-critical buses

- Implement proper spacing for differential pairs

7.2 Clock Distribution

Clock signals require special attention:

- Use dedicated layers for critical clock distribution

- Implement proper termination for clock lines

- Consider clock tree synthesis for large systems

- Shield clock traces when necessary

8. Design Verification and Testing

8.1 Simulation and Analysis

- Perform signal integrity simulations before fabrication

- Analyze power delivery network performance

- Conduct thermal analysis for high-power designs

- Verify EMC compliance through simulation

8.2 Prototype Testing

- Include test points for critical signals

- Plan for rework and debugging

- Implement measurement capabilities in the design

- Consider design iterations in the project timeline

Conclusion

Designing high-speed multilayer PCBs requires a holistic approach that balances electrical performance, thermal management, manufacturability, and cost. By addressing signal integrity from the initial design stages, carefully planning the layer stackup, implementing robust power distribution, and considering EMC implications throughout the process, designers can create successful high-speed multilayer PCB designs. As signal speeds continue to increase and electronic systems become more complex, these considerations will only grow in importance. Staying current with design techniques, simulation tools, and manufacturing capabilities is essential for engineers working in this challenging and rewarding field.

Remember that each design presents unique challenges, and there is rarely a one-size-fits-all solution. The most successful high-speed PCB designers combine theoretical knowledge with practical experience, continually refining their approach based on measurement results and real-world performance. By paying attention to the factors outlined in this article and maintaining close collaboration with fabrication and assembly partners, designers can significantly increase their chances of first-pass success in high-speed multilayer PCB projects.