The key to PCB layout! Teach you to get PCB layout right in one go

Today’s switching regulators and power supplies are more sophisticated and powerful, but one of the challenges they face is that the ever-increasing switching frequency makes PCB design more difficult. PCB layout is becoming a watershed that distinguishes a good switching power supply design from a bad one. This article will provide suggestions on how to achieve a good PCB layout the first time.

Take a 3A switching regulator that reduces 24V to 3.3V as an example. At first glance, a 10W regulator wouldn’t be too difficult, so designers are usually tempted to jump right into the construction phase.

However, using design software such as National Semiconductor’s Webench, we can observe what problems this idea actually encounters

After entering the above requirements, Webench will select the LM25576 (a 42V input component including 3AFET) from the company’s ‘SimplerSwitcher’ series. It is packaged in a TSSOP-20 with a thermal pad.

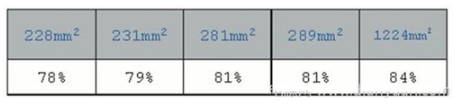

Webench options include optimizing the design for either size or efficiency, all in a single option. That is, high efficiency requires low switching frequency (reducing switching losses in the FETs). Therefore, large inductors and capacitors are required, which requires more PCB space.

Note: The highest efficiency is 84%, and this highest efficiency is achieved when the input-output voltage difference is low. In this case, the input/output ratio is greater than 7. In general, using two stages reduces the stage-to-stage ratio, but the efficiency obtained through two regulators is not better.

Next, we choose the highest switching frequency with the smallest PCB area. High switching frequencies are most likely to cause problems in layout. Webench then generates a circuit diagram with all active and passive components.

Circuit Design

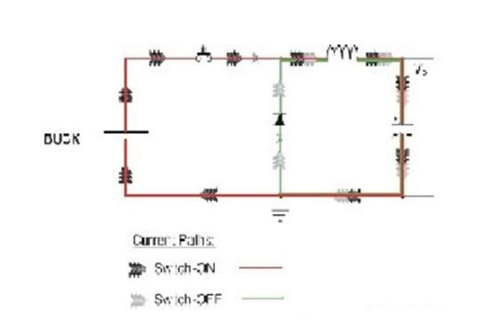

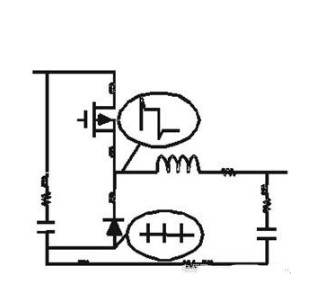

Refer to the current path in Figure 1: the path through which the FET flows when it is on is marked in red; the loop through which the FET flows when it is off is marked in green. We observe two different situations: areas with two colors and areas with only one color. We must pay special attention to the latter case, because the current alternates between zero and full-scale voltage. These are all high di/dt areas.

Figure 1

Alternating current with high di/dt generates a large magnetic field around the PCB traces, which is a major source of interference to other components in the circuit and even other circuits on the same or adjacent PCB. Since the common current path is assumed to be non-alternating, it is not a critical path and the effect of di/dt is much smaller. On the other hand, these areas are more loaded over time. In this case, the common path is from the cathode of the diode to the output and from the output ground to the anode of the diode. The output capacitor has a very high di/dt when it charges and discharges. All the lines connecting the output capacitor must meet two conditions: they should be wide due to the high current; and they should be as short as possible to minimize the effect of di/dt.

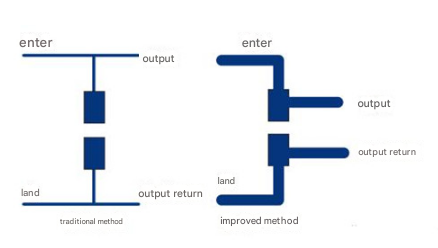

Figure 2

In fact, designers should not use the so-called traditional layout method of leading wires from Vout and ground to the capacitor. These wires should be flowing with large AC current. It is a better method to connect the output and ground directly to the capacitor terminals. Therefore, the alternating current only appears on the capacitor. The other wires connecting the capacitor now carry an almost constant current and any problems with di/dt are solved.

Figure 3

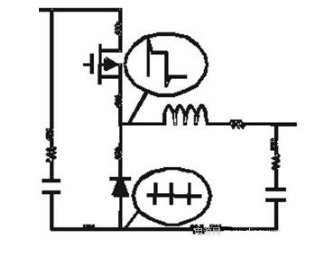

Ground design is another common area of misunderstanding. Simply putting a ground plane on ‘level 2’ and connecting all ground connections to it will not give good results.

Figure 4

Let’s see why. Our design example shows that up to 3A of current must flow from ground back to the source (a 24V car battery or a 24V power supply). There will be large currents in the ground connections of the diode, COUT, CIN and the load. The switching regulator ground connection carries a small current. The same applies to the ground reference of the resistor divider. If all of the above ground pins are connected to a ground plane, we will experience ground bouncing. Although small, the inductive points in the circuit (such as the resistor divider from which the feedback voltage is obtained) will not have a stable reference ground. As a result, the overall regulation accuracy will be greatly affected. In fact, we even get ‘ringing’ from the ground plane hidden in level 2, which is very difficult to locate.

In addition, high current connections must use vias to the ground plane, which is another source of interference and noise. It is a better solution to use the CIN ground connection as a star node for all high current ground traces on the input and output sides of the circuit. The star node connects the ground plane and the two low current ground connections (IC and voltage divider).

Figure 5

Now the ground plane is clean: no high currents, no ground bounce. All high current grounds are connected to the CIN ground in a star shape. All the designer has to do is to make the ground traces (all on the first layer of the PCB) as short and thick as possible. In this context, saving copper will basically not get good results.

Node impedance

High impedance nodes should be checked because they are easily interfered.

The most critical node is the feedback pin of the IC, whose signal is taken from the resistor divider. The FB pin is the input of an amplifier (such as the LM25576) or a comparator (such as in the case of a hysteretic regulator). In both cases, the impedance of the FB point is quite high. Therefore, the resistor divider should be placed to the right of the FB pin, and a short wire should be connected from the middle of the resistor divider to FB. The wire from the output to the resistor divider is low impedance and can be connected to the resistor divider with a longer wire. The focus here is on the wiring method rather than the wire length.

Other nodes are not so critical. So don’t worry about the switch node, the diode, COUT, the VIN pin of the switch IC, or CIN.

Wiring Tips

Wiring techniques make a difference for the resistor divider. The wire runs from COUT to the resistor divider and its ground returns to COUT. We must ensure that this loop does not form an open area. An open area will act as a receiving antenna. If we can ensure that the ground plane under the wire is not disturbed, then the area formed by the wire and the ground under it and between level 1 and level 2 should be undisturbed. Now, we can see why the ground should not be placed at level 4, because the distance is significantly increased.

Alternatively, the ground connection of the resistor divider can be routed to level1, making the two wires parallel and as close together as possible to make the area smaller. These observations apply to all wires through which the signal flows: sensor connection, amplifier output, input to the ADC or audio power amplifier. For every analog signal, it should be treated so that it is not easy to introduce noise.

This requirement to minimize the open area whenever possible also applies to low-impedance wires; in this case, we have a potential source (antenna) to transmit interference signals to other parts of the PCB or other devices. Note: the smaller the open area, the better.

The following two wires are also critical: from the switch output of the IC to the diode and inductor node; and from the diode to the node. Both of these wires have high di/dt: whether the switch is turned on or the diode flows current, so the wire should be as short and thick as possible. The wire from the node to the inductor and from the inductor to COUT is less critical. In this case, the inductor current is relatively constant and changes slowly. What we want to do is to make sure it is a low impedance point to minimize voltage drop.

Actual layout

Let’s take a look at a good layout (below). The main component is a controller in an MSOP-8 package used with an external FET.

Observe the space around CIN. Note: The ground point of this capacitor is directly connected to the anode of the diode. You cannot make the trace in the ‘power ground’ too short! The FET [SW] should be moved up a few millimeters to shorten the cathode-inductor-FET trace.

The COUT area is not visible. But we can observe that the resistor divider (FB1-FB2) is very close to the IC. FB2 is connected to another ground plane, and the ground pin of the IC is treated the same way. The ‘signal’ ground is connected to the ground plane with three vias, and the ‘power’ ground is also connected to the GND pin of the PCB with three vias. This way, the ‘signal’ ground will not ‘see’ any ground bounce of the ‘power’ ground.

If you follow a few simple rules (only some of which are discussed in this article), you will have no trouble with your PCB layout. Thinking carefully about the PCB layout before you start will help save time and effort in dealing with switching power supply anomalies.