Design of reconfigurable speed measurement module based on FPGA

1 Reconfigurable principle based on FPGA

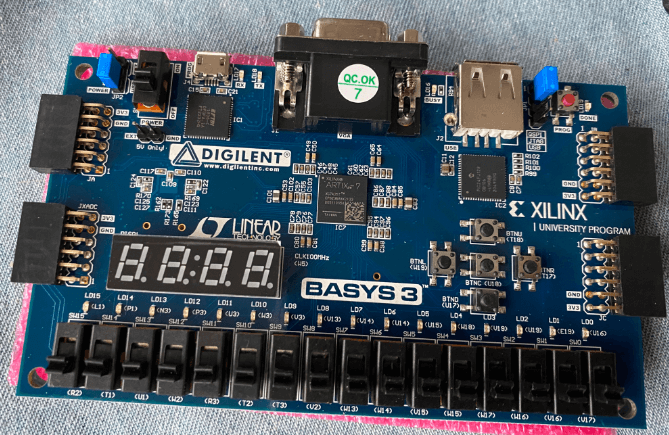

FPGA (field programmable gate array) is a programmable logic device, which is developed on the basis of PAL, GAL and other logic devices. Compared with the previous PAL, GAL, etc., FPGA is much larger in scale, while the cost per logic gate is much lower. The high capacity and low cost create conditions for the application of FPGA in printing system. FPGA can realize I/O processing, pulse generation, counting, mathematical operation and other functions, which can greatly simplify the design of numerical control system.

The biggest feature of FPGA is the online reconfigurability of its internal logic.

At present, the mainstream FPGA is based on the lookup table structure. The lookup table (160kUP Table) is referred to as LUT. LUT is essentially a RAM. As shown in Figure 1. In the design of CMOS separation logic circuit, the method of Figure 1 (a) is usually used to realize the inverter. However, in FPGA, LUT is used to realize this function, as shown in Figure 1 (b). The control input SEL of MUX is used as the logic input, while IN1 and IN2 are the lookup tables of the inverter. There are two reasons for this:

1) LUT is universal and can implement any logic.

2) LUT can be efficiently implemented on silicon.

Due to the volatility of SRAM, the FPGA needs to be configured after the system is powered on to put the FPGA into working state. The configuration information is usually stored in PROM or FLASH memory, but other devices, such as CPU, can also be used to complete this task. Therefore, the CPU can be used to configure the FPGA and store the configuration information in the memory of the CPU system, which not only reduces the cost, but also allows different configuration information to be selected according to actual needs. Since the configuration process is very short, usually within a few hundred milliseconds, the FPGA can be reconfigured during the system operation to achieve real-time reconfiguration.

2 Output waveform of photoelectric encoder and its speed measurement method

Photoelectric encoders usually output two square waves A and B with a phase difference of 90°. Depending on the direction of rotation, A phase may lead B phase. When using photoelectric encoders to measure speed, three major functions need to be completed: false count suppression, direction identification and speed measurement.

In terms of false count suppression, there are analog and digital methods.

The analog method [1] uses an RC circuit to convert the square wave signal transmitted by the encoder into a pulse signal. The digital method often uses a D flip-flop [2, 3, 4] to delay the square wave signal and then perform logical operations on the delayed waveform. Based on the logical relationship of the 90° phase difference between the two waveforms, the miscounting caused by jitter or interference and the influence of glitches caused by oscillation or circuit interference are eliminated. The number of stages used in the D flip-flop has a direct relationship with the suppression of miscounting [2]. In the case of severe interference, an encoder with a long-line drive interface can be selected. It divides the A and B phase signals into four signal lines A, A and B, B using RS 422 (differential mode) for transmission. This can effectively suppress common-mode interference and increase the transmission distance.

The algorithms for the speed measurement function mainly include the M method, T method, M/T method, and M and T methods.

Both the M method and the T method are simple and easy to implement, but the accuracy is affected by the speed. The M/T method has higher accuracy. The M/T method and the variable M/T method are currently recognized as high-precision speed measurement methods.

There are mainly pure hardware, pure software, and a combination of hardware and software. The advantage of the pure hardware method [2, 5] is that it can be completed automatically without CPU intervention, but the disadvantage is that there are many peripheral devices and only the M method and T method can be implemented. The signal line of the pure software [6] method is connected to the CPU interrupt input and I/O port. The advantage is that fewer external devices are used, but the disadvantage is that it takes up too much CPU time and the measurement accuracy is not high. For example, the clock frequency of 80C196 is 12 MHz. After frequency division, the reference frequency of the T1 timer is 0.75 MHz. Regardless of whether the M method, T method, or M/T method is used, the accuracy is limited by the reference frequency and cannot be further improved. However, FPGA can greatly increase the reference frequency, which can essentially improve the accuracy of speed measurement. The combination of hardware and software [3, 4] is that the functions of false counting suppression and phase detection are completed by external hardware circuits, while the counting function is completed by the CPU. It is a compromise between the above two methods, but the accuracy is still limited. ?

3 Reconfigurable design using FPGA

In summary, by utilizing the programmable and reconfigurable features of FPGA, the logic circuits that were previously designed separately can be integrated into the system by utilizing the rich logic resources inside FPGA and the strong gate-level circuit description features of VerilogHDL. Various speed measurement methods can be implemented according to the requirements of the application without the intervention of the CPU. It can be embedded in the system as a functional module, and different speed measurement methods can be selected according to different needs without modifying the hardware circuit to achieve reconstruction.

1) Implementation of M-method reconfigurable design?

Imitate the structure of traditional D flip-flop + counter, as shown in Figure 2. Two 4-level D flip-flops in series are constructed through VerilogHDL. The error suppression circuit (encode module in Figure 2) and the direction detection circuit are constructed. At the same time, the Mega Function function provided by Quarts is used to implement a 16-bit synchronous reversible counter (lpm_couter module in Figure 2) and a 16-bit latch (d module in Figure 2) to complete the M-method speed measurement logic circuit for the encoder pulse.

The simulation results are shown in Figure 3. The CHA and CHB signals enter the FPGA. After the delay of the third and fourth triggers, the wave behaviors are A3, A4 and B3, B4 respectively. After the direction identification, the DIR and REV signals are obtained, and the frequency of these two signals is 4 times that of the original A phase or B phase. For the convenience of explanation, the counter in Figure 3 only measures the number of clocks in a signal (DIR or REV) cycle. Since the value of the counter will be reset after each measurement, the value of the counter must be latched so that the CPU reads the effective speed (module d in Figure 2). As can be seen from Figure 3, after passing through the d module, the speed_out signal is output stably. In this example, the frequency of the reference clock signal CLOCK is 50 MHz.

2) Implementation of reconfigurable M/T method

Since the advantages of the M method and the T method are combined, the speed measurement is more accurate. The disadvantage is that a large number of peripheral chips need to be expanded and the interrupt of the microcontroller is occupied, and the programming is relatively complex [5]. The M/T speed measurement logic is realized by using the rich logic resources inside the FPGA and the finite state machine method. The state machine is a hardware sequential circuit composed of combinational circuits and sequential circuits. The state transfer depends on the current state and the input state of the state machine. This state machine is a Mealy type state machine; the state transfer depends only on the current state is called a Moore type state machine. Moore type state machine can be regarded as a special case of Mealy type state machine.

This design adopts Mealy type state machine. After receiving the reset signal, the state machine enters the (00) state. In the (00) state, the reset of timer ?T and the reset of m1 and m2 counters are mainly completed. When the first pulse arrives, the state machine enters the (01) state. At this time, timer T starts to count, and m1 and m2 start counting at the same time. After Tg expires, it enters the (10) state. At this time, m1 and m2 continue to count. When the last pulse arrives, it enters the (11) state. After the values of m1 and m2 are latched into the latch, it automatically resets to the (00) state.

Using the idea of modular design, the speed measurement logic is divided into four parts, among which the pluse_couter and clock_couter counters are adder counters constructed using the Mega Function function provided by Quarts, which respectively complete the counting function of the encoder pulse m1 and the reference clock pulse m2.

The Encode module completes the control of the direction detection signals REV and DIR, latch signal LOCK, counter reset signal COUTER_RST, and direction signal UPDOWN of the encoder signals CHA and CHB. The D_TRIGGER unit completes the latching of the results of the two counters, and at the same time combines the UP_DOWN signal and the result (7 bits) measured by the encoder pulse counter to form an 8-bit PULSE_D. The pulse value obtained in this way is the number of directional pulses. The outputs PULSE_D[7.0] and CLOCK_D[15.0] of D_TRIGGER are the final measured results. The final simulation results are shown in Figure 7. A 50 MHz reference signal is used, and CHA and CHB are 0.5 MHz square waves with a phase difference of 90°. The two-phase signal is quadrupled to obtain two direction pulse signals, DIR and REV. Under the control of the finite state machine (STA), the lock signal (LOCK), the counter reset signal (COUTER_RST) and the two counter units PULSE_NUM_OUT and CLOCK_NUM_OUT work according to the predetermined timing, meeting the design requirements. After the program is compiled, a total of 68 logic cells are occupied, with a maximum delay of 13.8 ns.

4 Conclusion

The reconfigurable characteristics of FPGA are used to reduce peripheral devices and simplify the design of CPU programs. The M method, T method, and M/T method can be flexibly selected according to the requirements of the site. This embedded design method can also be used for speed measurement circuits such as the variable M/T method and the direct frequency measurement method. By constructing an interface with the CPU, the FPGA is accessed like an external RAM for the CPU, and no intervention is required in the speed measurement process. At the same time, if the speed measurement time and reference frequency are designed as externally controllable parameter units, the parameters can be easily modified to achieve higher-precision control in different occasions and under different requirements.