High-Speed PCB Design Strategies: A Comprehensive Guide

Introduction

In today’s fast-evolving electronics industry, high-speed printed circuit board (PCB) design has become a critical aspect of ensuring signal integrity, power integrity, and electromagnetic compatibility (EMC). As data rates continue to increase—driven by advancements in computing, telecommunications, and IoT—designers must adopt robust strategies to mitigate signal degradation, crosstalk, and power delivery issues.

This article explores key high-speed PCB design strategies, covering signal integrity, power distribution, layer stack-up, routing techniques, and simulation tools. By following these best practices, engineers can optimize performance and reliability in high-speed digital systems.

1. Understanding Signal Integrity in High-Speed PCB Design

Signal integrity (SI) refers to the quality of electrical signals as they travel through PCB traces. At high frequencies, factors such as impedance mismatches, reflections, and crosstalk can degrade signal performance.

1.1 Controlled Impedance Routing

High-speed signals (e.g., DDR, PCIe, USB 3.0+) require controlled impedance to minimize reflections. Key considerations include:

- Trace Width and Spacing: Use PCB stack-up calculators to determine proper trace dimensions for target impedance (e.g., 50Ω single-ended, 100Ω differential).

- Reference Planes: Ensure uninterrupted ground/power planes beneath signal layers to maintain consistent impedance.

1.2 Minimizing Signal Reflections

Reflections occur due to impedance discontinuities. Mitigation techniques include:

- Proper Termination: Use series or parallel termination resistors to match impedance.

- Avoiding Stubs: Use via-in-pad or microvia techniques for high-speed signals to reduce stub effects.

1.3 Managing Crosstalk

Crosstalk arises when signals interfere with adjacent traces. Solutions include:

- 3W Rule: Space traces at least three times the trace width apart to reduce coupling.

- Differential Pair Routing: Maintain tight coupling in differential pairs while increasing spacing from other signals.

2. Power Integrity and Distribution Network Design

Power integrity (PI) ensures stable voltage delivery to high-speed components. Poor PI leads to noise, ground bounce, and timing errors.

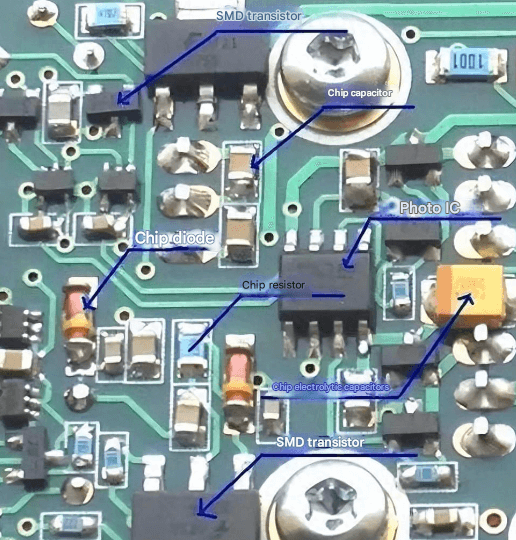

2.1 Decoupling Capacitors

- Placement: Place decoupling capacitors as close as possible to IC power pins.

- Value Selection: Use a mix of bulk (10μF), mid-range (0.1μF), and high-frequency (1nF) capacitors.

2.2 Power Plane Design

- Low-Inductance Planes: Use thin dielectric layers between power and ground planes to reduce loop inductance.

- Split Planes: Avoid splitting power planes for high-speed signals to prevent return path discontinuities.

2.3 PDN Impedance Optimization

- Target a low impedance across a wide frequency range using simulation tools like Ansys SIwave or Cadence Sigrity.

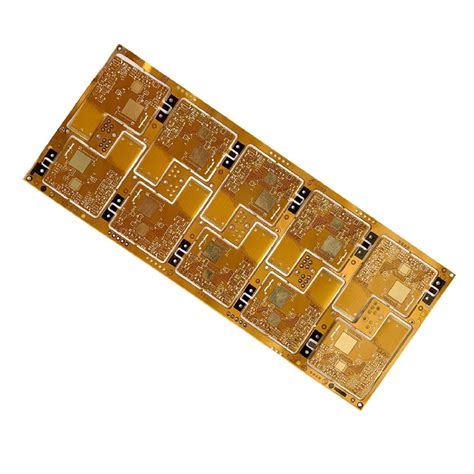

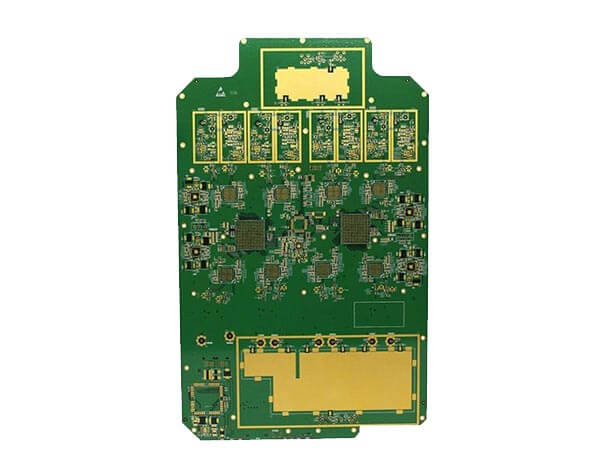

3. PCB Stack-Up and Layer Planning

A well-designed layer stack-up minimizes EMI and ensures signal integrity.

3.1 Recommended Stack-Up for High-Speed PCBs

A typical 6- or 8-layer stack-up may include:

- Top Layer: High-speed signals

- Ground Plane

- Signal Layer (with adjacent reference plane)

- Power Plane

- Signal Layer

- Bottom Layer (low-speed signals or power)

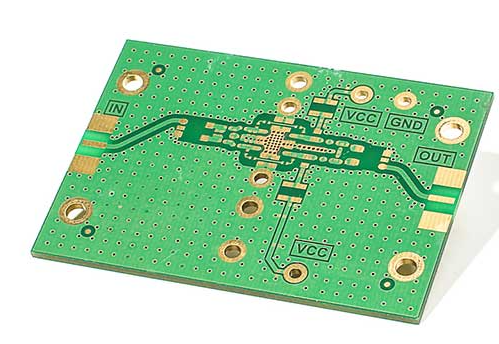

3.2 Microstrip vs. Stripline Routing

- Microstrip (outer layers): Faster propagation but more susceptible to EMI.

- Stripline (inner layers): Better EMI shielding but higher propagation delay.

4. High-Speed Routing Techniques

4.1 Length Matching

High-speed buses (e.g., DDR, SerDes) require matched trace lengths to avoid skew.

- Trombone and Serpentine Routing: Use meandering traces to match delays.

4.2 Via Optimization

- Minimize Via Stubs: Use back-drilling or blind/buried vias.

- Via Count Reduction: Fewer vias reduce impedance discontinuities.

4.3 Differential Pair Routing

- Maintain Consistent Spacing: Avoid gaps between pairs to prevent mode conversion.

- Avoid 90° Bends: Use 45° or curved traces to minimize impedance variations.

5. EMI/EMC Considerations

5.1 Grounding Strategies

- Solid Ground Planes: Provide low-impedance return paths.

- Partitioning: Separate analog and digital grounds but connect at a single point.

5.2 Shielding and Filtering

- Guard Traces: Place grounded traces near sensitive signals.

- Ferrite Beads/Common-Mode Chokes: Suppress high-frequency noise.

6. Simulation and Validation

6.1 Pre-Layout Simulation

- Use tools like HyperLynx or Keysight ADS to model signal behavior before routing.

6.2 Post-Layout Analysis

- Perform S-parameter extraction, eye diagram analysis, and TDR measurements.

6.3 Prototype Testing

- Use vector network analyzers (VNAs) and oscilloscopes for real-world validation.

Conclusion

High-speed PCB design demands a systematic approach, balancing signal integrity, power distribution, and EMI control. By implementing controlled impedance routing, optimizing power delivery, and leveraging simulation tools, engineers can achieve robust, high-performance designs.

As technology advances, staying updated with emerging standards (e.g., PCIe 6.0, DDR5) and design methodologies will be crucial for success in high-speed PCB development.

This article provides a foundation for mastering high-speed PCB design. For further learning, explore industry resources such as High-Speed Digital Design by Howard Johnson and Signal and Power Integrity by Eric Bogatin.

Would you like additional details on any specific aspect of high-speed PCB design?