Signal Return Paths in High-Speed PCB Design: Principles and Best Practices

Abstract

This paper explores the critical aspects of signal return paths in high-speed printed circuit board (PCB) design. As digital systems continue to operate at higher frequencies with faster edge rates, proper management of return currents becomes essential for maintaining signal integrity, minimizing electromagnetic interference (EMI), and ensuring reliable system operation. The discussion covers fundamental concepts, analysis techniques, and practical design guidelines for optimizing return paths in modern high-speed designs.

1. Introduction

In high-speed PCB design, signal integrity engineers traditionally focus on the visible signal traces while often overlooking the equally important return current paths. However, as clock frequencies exceed hundreds of megahertz and rise times fall into the picosecond range, the return path becomes a dominant factor in determining overall system performance.

All electrical currents must flow in closed loops, and high-frequency signals naturally seek the path of least impedance (not just resistance) back to their source. This paper examines how these return currents behave in various PCB configurations and provides design methodologies to control their effects.

2. Fundamental Concepts of Return Currents

2.1 Current Loop Theory

Every electrical signal requires a complete circuit to flow. In PCB interconnects:

- The forward current travels along the signal trace

- The return current flows through some conductive path back to the source

At DC and low frequencies, return currents follow the path of least resistance, which may be any available conductor. However, at high frequencies (typically above 1 MHz), return currents follow the path of least impedance, which generally means staying close to the signal trace to minimize loop area.

2.2 Skin Effect and Current Distribution

At high frequencies, the skin effect causes currents to concentrate near the surface of conductors. This phenomenon affects return current distribution:

- In solid planes, return currents concentrate directly beneath signal traces

- The current density decreases exponentially with distance from the trace

- Approximately 90% of the return current flows within a width equal to three times the trace-to-plane separation

2.3 Frequency-Dependent Return Path Behavior

Return path characteristics change significantly with frequency:

- DC to ~1 MHz: Current spreads throughout available conductors

- 1 MHz to 100 MHz: Current begins to concentrate under traces

- Above 100 MHz: Current tightly couples to signal trace, following beneath it

3. Return Path Discontinuities and Their Effects

3.1 Common Discontinuities

Return path discontinuities occur when the ideal low-impedance path beneath a signal trace is interrupted:

- Gaps in reference planes

- Changes in reference plane layers (e.g., switching from ground to power)

- Slots or splits in planes

- Connectors and vias between layers

3.2 Signal Integrity Impacts

Discontinuities force return currents to find alternative paths, causing:

- Increased loop inductance leading to signal ringing and overshoot

- Crosstalk between adjacent signals sharing return paths

- Ground bounce and power supply noise

- Radiated emissions due to large loop areas

3.3 EMI Consequences

Poor return path management creates:

- Unintended antenna structures formed by large current loops

- Increased radiated emissions that may exceed regulatory limits

- Susceptibility to external interference

4. Return Path Analysis Techniques

4.1 Current Density Mapping

Modern 3D electromagnetic field solvers can visualize return current distribution:

- Identify areas of high current concentration

- Locate unintended return path bottlenecks

- Verify effectiveness of decoupling strategies

4.2 Loop Inductance Calculations

Key parameters to evaluate:

- Partial inductance of signal and return paths

- Mutual inductance between adjacent current loops

- Effective loop area for radiation estimation

4.3 Impedance Analysis

Critical measurements include:

- Return path impedance versus frequency

- Transfer impedance between different return nodes

- Plane impedance profiles

5. Design Guidelines for Optimal Return Paths

5.1 Reference Plane Management

- Maintain continuous reference planes beneath critical signals

- Avoid splits or gaps in high-speed signal return paths

- Use multiple vias to connect reference planes at transitions

5.2 Layer Stackup Considerations

- Place high-speed signals adjacent to solid reference planes

- Minimize dielectric thickness between signal and reference planes

- Use symmetrical stackups to balance return current distribution

5.3 Handling Plane Changes

When signals must change reference planes:

- Provide closely spaced decoupling capacitors between planes

- Use overlapping planes where possible

- Place transition vias immediately adjacent to signal vias

5.4 Mixed-Signal Designs

- Implement proper partitioning of analog and digital grounds

- Provide controlled return paths across partitions

- Use bridge connections between ground regions when necessary

5.5 Connector and Via Transitions

- Include adequate ground pins/pads in connectors

- Use ground vias adjacent to signal vias

- Consider return path continuity in backplane designs

6. Advanced Return Path Techniques

6.1 Embedded Capacitance

- Utilize power-ground plane capacitance for high-frequency decoupling

- Implement ultra-thin dielectrics for low-impedance plane pairs

- Design distributed capacitance into the stackup

6.2 Return Path Compensation

- Add intentional return vias near discontinuities

- Implement stitching capacitors across plane splits

- Use coplanar waveguide structures where plane references are unavailable

6.3 Differential Pair Considerations

- Maintain consistent reference plane coupling for differential signals

- Avoid asymmetrical return path conditions

- Properly terminate common-mode return currents

7. Measurement and Verification Methods

7.1 Time Domain Reflectometry (TDR)

- Identify impedance variations caused by return path issues

- Locate discontinuities along transmission lines

- Measure effective loop inductance

7.2 Vector Network Analysis

- Characterize return loss and insertion loss

- Identify resonances in return path structures

- Measure transfer impedance between reference points

7.3 Near-Field Scanning

- Visualize current distribution in operating boards

- Identify unintended return current paths

- Locate EMI hot spots

8. Case Studies

8.1 DDR Memory Interface

Analysis of return path effects on:

- Signal skew in byte lanes

- Write leveling accuracy

- Data eye closure

8.2 Multi-Gigabit SerDes Channels

Return path considerations for:

- XAUI interfaces

- PCI Express Gen 3/4

- 100G Ethernet implementations

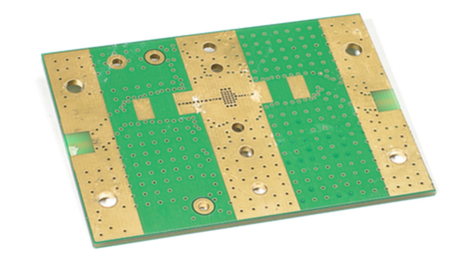

8.3 RF Module Integration

Mixed-signal return path challenges in:

- Cellular radio front ends

- Millimeter-wave circuits

- Phased array systems

9. Future Trends and Challenges

9.1 Higher Frequency Materials

- Low-loss dielectrics for millimeter-wave applications

- Ultra-thick copper for reduced plane impedance

- Advanced via structures for 3D interconnects

9.2 3D Packaging Technologies

- Return path management in silicon interposers

- Through-silicon via (TSV) return current distribution

- Die-to-die interface considerations

9.3 Photonic Integration

- Mixed electrical-optical return paths

- Grounding considerations for optoelectronic devices

- Return path continuity in hybrid assemblies

10. Conclusion

Proper management of signal return paths represents one of the most critical yet frequently overlooked aspects of high-speed PCB design. As data rates continue to increase and rise times decrease, return current behavior will play an even more significant role in determining system performance. By applying the principles and techniques discussed in this paper, designers can avoid common pitfalls and create robust high-speed designs that meet stringent signal integrity and EMC requirements.

The most effective high-speed designs treat return paths with the same level of attention as signal traces, recognizing that both elements form equally important parts of the complete current loop. Future design challenges will require even more sophisticated approaches to return path management as electronic systems push into higher frequency regimes and more complex 3D packaging architectures.