How to Reduce Inductance in High-Speed PCB Routing

Introduction

In the realm of high-speed printed circuit board (PCB) design, inductance management has become a critical factor affecting signal integrity, power delivery, and overall system performance. As digital systems push into the multi-gigahertz range with faster edge rates, the parasitic inductance that was once negligible can now cause significant signal degradation, power rail collapse, and electromagnetic interference (EMI) problems.

This article provides a comprehensive guide to reducing inductance in high-speed PCB routing, covering fundamental concepts, design techniques, material considerations, and layout strategies that professional PCB designers can implement to optimize their high-speed designs.

Understanding Inductance in PCB Interconnects

The Nature of Parasitic Inductance

All PCB traces possess inherent inductance, which becomes particularly problematic at high frequencies. The inductance (L) of a straight trace can be approximated by:

L = 2l[ln(2l/w + t) + 0.5 + 0.2235(w + t)/l] nH

Where:

- l = length of the trace (cm)

- w = width of the trace (cm)

- t = thickness of the trace (cm)

This equation reveals that inductance increases with trace length and decreases with trace width—a fundamental relationship that informs many inductance reduction strategies.

Impact on Signal Integrity

Excessive inductance in high-speed circuits manifests in several ways:

- Signal ringing and overshoot: Caused by LC resonances in the transmission path

- Ground bounce: Voltage fluctuations in ground reference due to di/dt through inductance

- Power delivery network (PDN) impedance: Limits high-frequency current delivery to ICs

- Crosstalk: Mutual inductance between adjacent traces

- EMI radiation: High di/dt through inductive loops acts as efficient antennas

Fundamental Strategies for Inductance Reduction

1. Minimizing Loop Areas

The single most effective method for reducing inductance is minimizing current loop areas. Inductance is directly proportional to the area enclosed by current flow:

L ∝ A

Where A is the loop area. This principle applies to:

- Signal-return current paths

- Power-ground current loops

- Decoupling capacitor mounting

Implementation techniques:

- Place ground returns immediately adjacent to signal traces

- Use closely spaced power-ground plane pairs

- Route differential pairs with tight coupling

- Place decoupling capacitors to minimize via loop areas

2. Proper Use of Reference Planes

Solid reference planes provide the lowest inductance return paths:

- Maintain unbroken ground planes beneath high-speed traces

- Use multiple vias to connect to reference planes when layer changing

- Avoid splits or gaps in reference planes under critical traces

- For power, use thin dielectric power-ground plane pairs for inherent capacitance

3. Optimizing Trace Geometry

Trace dimensions significantly affect inductance:

- Width: Wider traces have lower inductance (but higher capacitance)

- Length: Shorter traces have proportionally less inductance

- Thickness: Thicker traces reduce inductance slightly

- Shape: Curved traces have slightly higher inductance than straight ones

Practical considerations:

- Use the widest practical trace for power distribution

- Keep high-speed traces as short as possible

- Avoid unnecessary meandering or serpentine routing

- Consider microstrip vs. stripline configurations based on needs

Advanced Inductance Reduction Techniques

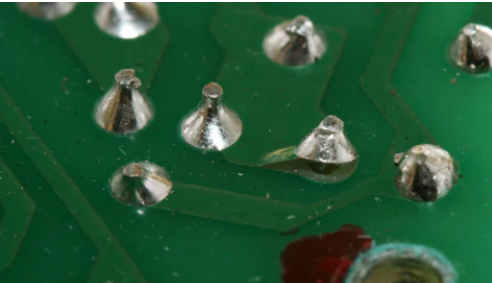

1. Via Optimization

Vias often contribute significant inductance in high-speed designs. The inductance of a via can be approximated by:

L_via ≈ 5.08h[ln(4h/d) + 1] pH

Where:

- h = via length (in mils)

- d = via diameter (in mils)

Reduction strategies:

- Use multiple vias in parallel for power/ground connections

- Minimize via length by using appropriate layer transitions

- Consider via-in-pad techniques for critical components

- Use larger diameter vias where possible

- Implement via stitching along transmission lines

2. Power Delivery Network (PDN) Design

The PDN often represents the most challenging inductance management problem:

- Implement closely spaced power-ground plane pairs (3-4 mil spacing)

- Use distributed decoupling with multiple capacitor values

- Place bulk capacitors strategically to service multiple ICs

- Consider embedded capacitance materials for ultra-high frequencies

- Implement proper via placement for capacitor mounting

3. Transmission Line Techniques

Proper transmission line implementation controls inductance effects:

- Maintain consistent impedance along the entire route

- Use appropriate termination to prevent reflections

- Consider differential signaling for critical high-speed nets

- Implement proper corner treatments (45° or curved bends)

- Use ground plane cutouts judiciously to manage inductance

Material and Stackup Considerations

Dielectric Selection

While primarily affecting capacitance, dielectric properties influence inductance:

- Lower εr materials allow wider traces for given impedance, reducing L

- Ultra-low loss materials minimize dispersion effects

- Thin dielectrics enable closer coupling to reference planes

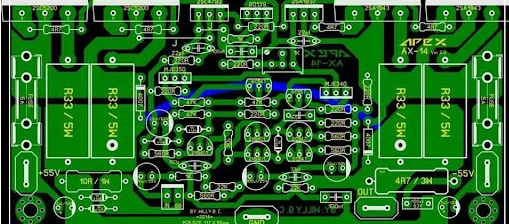

Layer Stackup Design

Optimal layer arrangements reduce inductance:

- Alternate signal layers between ground/power planes

- Use multiple ground planes for complex designs

- Consider dedicated power plane pairs for critical voltages

- Balance the stackup to prevent warpage while maintaining thin dielectrics

Special Considerations for Different Signal Types

1. Clock Signals

Clock distribution requires particular attention:

- Minimize trace length while maintaining matched lengths

- Use lower impedance traces (wider) where practical

- Implement tree structures with proper termination

- Consider clock buffer placement to minimize longest runs

2. High-Speed Serial Links

Differential pairs demand careful management:

- Maintain tight coupling between pair members

- Keep consistent spacing to reference planes

- Match lengths precisely (including vias)

- Implement proper differential termination

3. Power Distribution

Bulk power delivery challenges:

- Use planes rather than traces where possible

- Implement multiple parallel paths

- Consider thicker copper for high-current layers

- Use interleaved power-ground plane sandwiches

Verification and Measurement Techniques

Simulation Methods

- 3D electromagnetic field solvers for critical nets

- Transmission line calculators for initial estimates

- Power integrity analysis tools for PDN verification

- Signal integrity simulation for timing analysis

Measurement Approaches

- Time Domain Reflectometry (TDR) for impedance verification

- Vector Network Analyzer (VNA) measurements for S-parameters

- Power rail measurements with high-bandwidth probes

- Near-field scanning for EMI hotspot identification

Practical Design Examples

Case 1: DDR Memory Interface

- Implement tight ground return paths for each signal

- Use interleaved power-ground via stitching

- Maintain matched lengths with careful serpentine routing

- Place decoupling capacitors with minimal via inductance

Case 2: Multi-Gigabit Serial Link

- Use tightly coupled differential pairs

- Implement continuous reference planes beneath

- Minimize via transitions through proper layer assignment

- Apply appropriate pre-emphasis and equalization

Case 3: High-Current Power Distribution

- Use thick copper layers (2 oz or more)

- Implement multiple parallel vias for current sharing

- Distribute bulk capacitors strategically

- Monitor voltage drop through sense lines

Emerging Technologies and Future Trends

Advanced Materials

- Ultra-low loss dielectrics for longer reaches

- Embedded passive components for reduced parasitics

- Carbon-doped materials for improved plane capacitance

Novel Structures

- Electromagnetic bandgap (EBG) structures for noise suppression

- 3D interposers for ultra-short interconnects

- Optical interconnects for extremely high-speed links

Manufacturing Advances

- Laser-drilled microvias for dense interconnects

- Additive processes for optimized trace shapes

- Advanced via filling techniques for improved conductivity

Conclusion

Reducing inductance in high-speed PCB routing requires a holistic approach encompassing careful stackup design, proper material selection, strategic component placement, and meticulous routing techniques. By understanding the fundamental relationships between geometry and inductance, implementing proven reduction strategies, and verifying designs through simulation and measurement, PCB designers can successfully meet the challenges of modern high-speed digital systems.

The key principles—minimizing loop areas, optimizing return paths, careful via management, and proper power distribution—remain constant even as technologies evolve. Mastering these concepts enables designers to push performance boundaries while maintaining signal integrity in increasingly demanding applications.

As data rates continue to climb with new standards and technologies, inductance management will remain a cornerstone of successful high-speed PCB design, requiring ongoing education, careful analysis, and creative problem-solving from design professionals.